DSP56303VL100 Freescale Semiconductor, DSP56303VL100 Datasheet - Page 49

DSP56303VL100

Manufacturer Part Number

DSP56303VL100

Description

IC DSP 24BIT 100MHZ 196-MAPBGA

Manufacturer

Freescale Semiconductor

Series

DSP563xxr

Type

Fixed Pointr

Datasheet

1.DSP56303AG100.pdf

(108 pages)

Specifications of DSP56303VL100

Interface

Host Interface, SSI, SCI

Clock Rate

100MHz

Non-volatile Memory

ROM (576 B)

On-chip Ram

24kB

Voltage - I/o

3.30V

Voltage - Core

3.30V

Operating Temperature

-40°C ~ 100°C

Mounting Type

Surface Mount

Package / Case

196-MAPBGA

Device Core Size

24b

Format

Fixed Point

Clock Freq (max)

100MHz

Mips

100

Device Input Clock Speed

100MHz

Ram Size

24KB

Program Memory Size

Not RequiredKB

Operating Supply Voltage (typ)

3.3V

Operating Supply Voltage (min)

3V

Operating Supply Voltage (max)

3.6V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

196

Package Type

MA-BGA

Package

196MA-BGA

Maximum Speed

100 MHz

Device Million Instructions Per Second

100 MIPS

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DSP56303VL100

Manufacturer:

FUJI

Quantity:

1 000

Company:

Part Number:

DSP56303VL100

Manufacturer:

FREESCALE

Quantity:

672

Company:

Part Number:

DSP56303VL100

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

DSP56303VL100B1

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

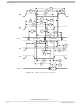

2.5.5.5 Asynchronous Bus Arbitration Timings

The asynchronous bus arbitration is enabled by internal synchronization circuits on

synchronization circuits add delay from the external signal until it is exposed to internal logic. As a result of this

delay, a DSP56300 part may assume mastership and assert

reason for timing 250.

Once

DSP56300 components that are potential masters on the same bus. If

is asserted and

Therefore, some non-overlap period between one

ensures that overlaps are avoided.

Freescale Semiconductor

250

251

Notes:

No.

BB

BB assertion window from BG input deassertion

Delay from BB assertion to BG assertion

1.

2.

3.

4.

5.

is asserted, there is a synchronization delay from

Bit 13 in the Operating Mode Register must be set to enter Asynchronous Arbitration mode.

If Asynchronous Arbitration mode is active, none of the timings in Table 2-14 is required.

An expression is used to compute the maximum or minimum value listed, as appropriate.

Asynchronous Arbitration mode is recommended for operation at 100 MHz.

In order to guarantee timings 250, and 251, BG inputs must be asserted to different DSP56300 devices on the same bus in the

non-overlap manner shown in Figure 2-26.

BB

is deasserted, another DSP56300 component may assume mastership at the same time.

BG1

BB

BG2

Figure 2-26.

Characteristics

Table 2-15.

5

DSP56303 Technical Data, Rev. 11

5

Asynchronous Bus Arbitration Timing

BG

Asynchronous Bus Timings

input active to another

BB

BB

250

assertion to the time this assertion is exposed to other

, for some time after

250+251

BG

input is asserted before that time, and

BG

Expression

251

1, 2

2.5 × Tc + 5

2 × Tc + 5

input active is required. Timing 251

BG

BG

is deasserted. This is the

AC Electrical Characteristics

3

and

BB

Min

inputs. These

—

25

100 MHz

Max

30

—

4

Unit

ns

ns

2-29

BG