MT9V032C12STC Aptina LLC, MT9V032C12STC Datasheet

MT9V032C12STC

Specifications of MT9V032C12STC

MT9V032C12STC ES

Q3986409

Related parts for MT9V032C12STC

MT9V032C12STC Summary of contents

Page 1

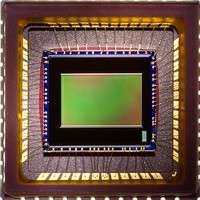

... Wide-VGA CMOS Digital Image Sensor MT9V032C12STM (Monochrome, Pb-Free) MT9V032C12STC (Color, Pb-Free) Features ® ® • Micron DigitalClarity CMOS imaging technology • Array format: Wide-VGA, active 752H x 480V (360,960 pixels) • Global shutter photodiode pixels; simultaneous integration and readout • Monochrome or color: Near_IR enhanced ...

Page 2

General Description The Micron Imaging MT9V032 is a 1/3-inch wide-VGA format CMOS active-pixel digital image sensor with global shutter and high dynamic range (HDR) operation. The sensor has specifically been designed to support the demanding interior and exterior unat- tended ...

Page 3

Figure 2: MT9V032 Quantum Efficiency vs. Wavelength 350 PDF: 09005aef824c9998/Source: 09005aef824c999c MT9V032_LDS_2.fm - Rev. B 3/07 EN MT9V032: 1/3-Inch Wide-VGA Digital Image Sensor 450 550 650 750 Wavelength (nm) Micron Technology, ...

Page 4

Pin Descriptions Figure 3 shows the package pinout for the MT9V032. Table 3 on page 5 provides the pin descriptions. Figure 3: 48-Pin CLCC Package Pinout Diagram LVDSGND BYPASS_CLKIN_N BYPASS_CLKIN_P SER_DATAIN_N SER_DATAIN_P LVDSGND PDF: 09005aef824c9998/Source: 09005aef824c999c MT9V032_LDS_2.fm - Rev. B ...

Page 5

Table 3: Pin Descriptions Only pins D 0 through D OUT Pin Number Symbol 29 RSVD 10 SER_DATAIN_N 11 SER_DATAIN_P 8 BYPASS_CLKIN_N 9 BYPASS_CLKIN_P 23 EXPOSURE 25 SCLK S_CTRL_ADR0 31 S_CTRL_ADR1 32 RESET# 33 STANDBY 47 SYSCLK ...

Page 6

Table 3: Pin Descriptions (continued) Only pins D 0 through D OUT Pin Number Symbol 35 VAAPIX 6 V LVDS LVDSGND 13 GND 34 GND ...

Page 7

Electrical Specifications Table 4: DC Electrical Characteristics V = 3.3V ±0.3V; T PWR A Symbol Definition V Input high voltage IH V Input low voltage IL I Input leakage current IN V Output high voltage OH V Output low voltage ...

Page 8

Table 6: LVDS Receiver DC Specifications V = 3.3V ±0.3V; T PWR A Symbol Definition V + Input differential IDTH Iin Input current Caution Stresses greater than those listed in Table 7 may cause permanent damage to the device. Table ...

Page 9

Package Dimensions Figure 5: 48-Pin CLCC Package Outline Drawing D Seating plane A 8.8 0.8 47X 4.4 TYP 1.0 ±0 48X 0.40 ±0.05 8.8 4.4 4X 0.2 5.215 5.715 11.43 Lead finish: Au plating, 0.50 microns minimum thickness ...

Page 10

Appendix A – Serial Configurations With the LVDS serial video output, the deserializer can meters from the sensor. The serial link can save on the cabling cost of 14 wires (D FRAME_VALID, PIXCLK, GND). Instead, just ...

Page 11

Configuration of Sensor for Stereoscopic Serial Output with Internal PLL In this configuration the internal PLL generates the shift-clk (x18) in phase with the system-clock. The LVDS pins SER_DATAOUT_P and SER_DATAOUT_N must be connected to a deserializer (clocked at approximately ...

Page 12

Broadcast and Individual Writes for Stereoscopic Topology In stereoscopic mode, the two sensors are required to run in lockstep. This implies that control logic in each sensor is in exactly the same state as its pair on every clock. To ...

Page 13

Revision History Rev ...