CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 11

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

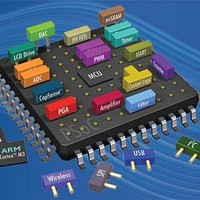

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

TMS

JTAG test mode select programming and debug port connection.

USBIO, D+

Provides D+ connection directly to a USB 2.0 bus. May be used

as a digital I/O pin; it is powered from V

Vddio. Pins are Do Not Use (DNU) on devices without USB.

USBIO, D–

Provides D– connection directly to a USB 2.0 bus. May be used

as a digital I/O pin; it is powered from V

Vddio. Pins are Do Not Use (DNU) on devices without USB.

Vboost

Power sense connection to boost pump.

Vbat

Battery supply to boost pump.

Vcca

Output of analog core regulator and input to analog core.

Requires a 1-µF capacitor to V

external use.

Vccd

Output of digital core regulator and input to digital core. The two

V

them as short as possible, and a 1-µF capacitor to V

Power System

Vdda

Supply for all analog peripherals and analog core regulator.

Vdda must be the highest voltage present on the device. All

other supply pins must be less than or equal to Vdda.

Vddd

Supply for all digital peripherals and digital core regulator. Vddd

must be less than or equal to Vdda.

Vssa

Ground for all analog peripherals.

Vssb

Ground connection for boost pump.

Vssd

Ground for all digital logic and I/O pins.

Vddio0, Vddio1, Vddio2, Vddio3

Supply for I/O pins. Each Vddio must be tied to a valid operating

voltage (1.71 V to 5.5 V), and must be less than or equal to Vdda.

If the I/O pins associated with Vddio0, Vddio2, or Vddio3 are not

used then that Vddio should be tied to ground (Vssd or Vssa).

XRES (and configurable XRES)

External reset pin. Active low with internal pull-up. Pin P1[2] may

be configured to be a XRES pin; see

(NVLs)”

Document Number: 001-11729 Rev. *R

CCD

pins must be shorted together, with the trace between

on page 22.

on page 29. Regulator output not for external use.

SSA

. Regulator output not for

“Nonvolatile Latches

DDD

DDD

instead of from a

instead of from a

SSD

; see

4. CPU

4.1 8051 CPU

The CY8C38 devices use a single cycle 8051 CPU, which is fully

compatible with the original MCS-51 instruction set. The

CY8C38 family uses a pipelined RISC architecture, which

executes most instructions in 1 to 2 cycles to provide peak

performance of up to 33 MIPS with an average of 2 cycles per

instruction. The single cycle 8051 CPU runs ten times faster than

a standard 8051 processor.

The 8051 CPU subsystem includes these features:

4.2 Addressing Modes

The following addressing modes are supported by the 8051:

4.3 Instruction Set

The 8051 instruction set is highly optimized for 8-bit handling and

Boolean operations. The types of instructions supported include:

Single cycle 8051 CPU

Up to 64 KB of flash memory, up to 2 KB of EEPROM, and up

to 8 KB of SRAM

Programmable nested vector interrupt controller

DMA controller

Peripheral HUB (PHUB)

External memory interface (EMIF)

Direct Addressing: The operand is specified by a direct 8-bit

address field. Only the internal RAM and the SFRs can be

accessed using this mode.

Indirect Addressing: The instruction specifies the register which

contains the address of the operand. The registers R0 or R1

are used to specify the 8-bit address, while the data pointer

(DPTR) register is used to specify the 16-bit address.

Register Addressing: Certain instructions access one of the

registers (R0 to R7) in the specified register bank. These

instructions are more efficient because there is no need for an

address field.

Register Specific Instructions: Some instructions are specific

to certain registers. For example, some instructions always act

on the accumulator. In this case, there is no need to specify the

operand.

Immediate Constants: Some instructions carry the value of the

constants directly instead of an address.

Indexed Addressing: This type of addressing can be used only

for a read of the program memory. This mode uses the Data

Pointer as the base and the accumulator value as an offset to

read a program memory.

Bit Addressing: In this mode, the operand is one of 256 bits.

Arithmetic instructions

Logical instructions

Data transfer instructions

Boolean instructions

Program branching instructions

PSoC

®

3: CY8C38 Family

Data Sheet

Page 11 of 129

[+] Feedback