CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 125

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

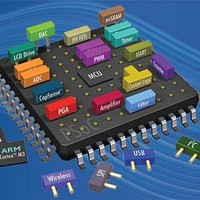

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

17. Revision History

Document Number: 001-11729 Rev. *R

Description Title: PSoC

Document Number: 001-11729

Rev.

*C

*D

*G

*H

*A

*B

*E

*F

*J

**

*I

ECN No.

2253366

2350209

2481747

2521877

2660161

2712468

2758970

2824546

2873322

571504

754416

Submission

®

See ECN

See ECN

See ECN

See ECN

See ECN

See ECN

02/16/09

05/29/09

09/02/09

12/09/09

02/04/10

3: CY8C38 Family Data Sheet Programmable System-on-Chip (PSoC

Date

Change

Orig. of

MKEA

MKEA

MKEA

MKEA

HMT

HMT

DSG

DSG

DSG

GDK

SFV

New data sheet for new device Part Number family.

Minor change: Added “Confidential” watermark. Corrected typo on 68QFN

pinout: pin 13 XREF to XRES.

Prelim3 release–extensive spec, writing, and formatting changes

Reorganized content to be consistent with the TRM. Added Xdata Space Access

SFRs and DAC sections. Updated Boost Converter section and Conversion

Signals section. Classified Ordering Information according to CPU speed;

added information on security features and ROHS compliance

Added a section on XRES Specifications under Electrical Specification.

Updated Analog Subsystem and CY8C35/55 Architecture block diagrams.

Updated Electrical Specifications. Renamed CyDesigner as PSoC Creator

Updates to Ordering Information table

and Tables). Updated GPIO and SIO AC specifications. Updated XRES Pin

Description and Xdata Address Map specifications. Updated DFB and

Comparator specifications. Updated PHUB features section and RTC in sleep

mode. Updated IDAC and VDAC DC and Analog Global specifications

Updated USBIO AC and Delta Sigma ADC specifications. Updated PPOR and

Voltage Monitors DC specifications. Updated Drive Mode diagram

Added 48-QFN Information. Updated other electrical specifications

and DC specs); also added Shottky Diode specs. Changed current for

sleep/hibernate mode to include SIO; Added footnote to analog global specs.

Updated Figures 1-1, 6-2, 7-14, and 8-1. Updated Table 6-2 and Table 6-3

(Hibernate and Sleep rows) and Power Modes section. Updated GPIO and SIO

AC specifications. Updated Gain error in IDAC and VDAC specifications.

Updated description of V

Current parameter. Updated number of UDBs on page 1.

Moved FILO from ILO DC to AC table.

Added PCB Layout and PCB Schematic diagrams.

Updated Fgpioout spec (Table 11-9). Added duty cycle frequency in PLL AC

spec table. Added note for Sleep and Hibernate modes and Active Mode specs

in Table 11-2. Linked URL in Section 10.3 to PSoC Creator site.

Updated Ja and Jc values in Table 13-1. Updated Single Sample Mode and Fast

FIR Mode sections. Updated Input Resistance specification in Del-Sig ADC

table. Added Tio_init parameter. Updated PGA and UGB AC Specs. Removed

SPC ADC. Updated Boost Converter section.

Added section 'SIO as Comparator'; updated Hysteresis spec (differential

mode) in Table 11-10.

Updated V

Added 'Bytes' column for Tables 4-1 to 4-5.

Updated PCB Schematic. Updated Figure 8-1 and Figure 6-3. Updated Interrupt

Vector table, Updated Sales links. Updated JTAG and SWD specifications.

Removed Jp-p and Jperiod from ECO AC Spec table. Added note on sleep timer

in Table 11-2. Updated ILO AC and DC specifications. Added Resolution

parameter in VDAC and IDAC tables. Updated I

values. Changed Temperature Sensor range to –40 °C to +85 °C. Removed

Latchup specification from Table 11-1.

Prepare Preliminary for PR1.

Prepare Preliminary2 for PR3--total rewrite.

Changed part numbers and data sheet title.

Updates to Electrical Specifications. Added Analog Routing section

Updated Part Numbering Conventions. Added Section 11.7.5 (EMIF Figures

Updated I2C section to reflect 1 Mbps. Updated Table 11-6 and 11- 7 (Boost AC

Changed maximum value of PPOR_TR to '1'. Updated V

BAT

condition and deleted Vstart parameter in Table 11-6.

DDA

Description of Change

spec in Table 11-1 and removed GPIO Clamp

PSoC

®

OUT

3: CY8C38 Family

®

)

typical and maximum

BIAS

Data Sheet

specification.

Page 125 of 129

[+] Feedback