CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 126

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

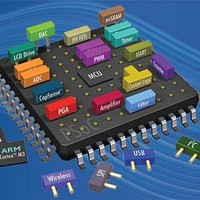

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

Document Number: 001-11729 Rev. *R

Description Title: PSoC

Document Number: 001-11729

*K

2903576

®

04/01/2010

3: CY8C38 Family Data Sheet Programmable System-on-Chip (PSoC

MKEA

Updated Tstartup parameter in AC Specifications table.

Added Load regulation and Line regulation parameters to Inductive Boost

Regulator DC Specifications table.

Updated I

In page 1, updated internal oscillator range under Precision programmable

clocking to start from 3 MHz.

Updated I

Updated Table 6-2 and Table 6-3.

Added bullets on CapSense in page 1; added CapSense column in Section 12.

Removed some references to footnote [1].

Changed INC_Rn cycles from 3 to 2 (Table 4-1).

Added footnote in PLL AC Specification table.

Added PLL intermediate frequency row with footnote in PLL AC Specs table.

Added UDBs subsection under 11.6 Digital Peripherals.

Updated Figure 2-6 (PCB Layout). Updated Pin Descriptions section and

modified Figures 6-6, 6-8, 6-9.

Updated LVD in Tables 6-2 and 6-3; modified Low-power modes bullet in page 1.

Added note to Figures 2-5 and 6-2; Updated Figure 6-2 to add capacitors for

V

Updated boost converter section (6.2.2).

Updated Tstartup values in Table 11-3.

Removed IPOR rows from Table 11-68.

Updated 6.3.1.1, Power Voltage Level Monitors.

Updated section 5.2 and Table 11-2 to correct suggestion of execution from

flash.

Updated V

Updated IDAC uncompensated gain error in Table 11-25.

Updated Delay from Interrupt signal input to ISR code execution from ISR code

in Table11-72. Removed other line in table.

Added sentence to last paragraph of section 6.1.1.3.

Updated T

Updated f_TCK values in Table 11-73 and f_SWDCK values in Table 11-74.

Updated SNR condition in Table 11-20.

Corrected unit of measurement in Table 11-21.

Updated sleep wakeup time in Table 6-3 and Tsleep in Table 11-3.

Added 1.71 V <= V

Removed mention of hibernate reset (HRES) from page 1 features, Table 6-3,

Section 6.2.1.4, Section 6.3, and Section 6.3.1.1.

Changed PPOR/PRES to TBDs in Section 6.3.1.1, Section 6.4.1.6 (changed

PPOR to reset), Table 11-3 (changed PPOR to PRES), Table 11-68 (changed

title, values TBD), and Table 11-69 (changed PPOR_TR to PRES_TR).

Added sentence saying that LVD circuits can generate a reset to Section 6.3.1.1.

Changed I

Changed resume time value in Section 6.2.1.3.

Changed ESD HBM value in Table 11-1.

Changed SNR in 16-bit resolution mode value and sample rate row in Table

11-20.

Removed V

Changed V

Changed INL max value in Table 11-27.

Added max value to the Quiescent current specs in Tables 11-29 and 11-31.

Changed occurrences of “Block” to “Row” and deleted the “ECC not included”

footnote in Table 11-57.

Changed max response time value in Tables 11-69 and 11-71.

Changed the Startup time in Table 11-79.

Added condition to intermediate frequency row in Table 11-85.

Added row to Table 11-69.

Added brown out note to Section 11.8.1.

Updated Vb pin in PCB Schematic.

DDA

and V

CC

OUT

RESP

DD

REF

IOFF

DDA

DDD

parameter in LCD Direct Drive DC Specs table.

values on page 1, page 5, and Table 11-2.

parameter in LCD Direct Drive DC Specs table.

specs in Table 11-21.

, high and low-power modes, in Table 11-24.

values and changed CMRR value in Table 11-23.

= 1.65 V rows and changed BWag value in Table 11-22.

pins.

DDD

< 3.3 V, SWD over USBIO pins value to Table 11-74.

PSoC

®

3: CY8C38 Family

®

)

Data Sheet

Page 126 of 129

[+] Feedback