CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 15

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

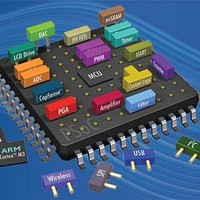

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow.

shows the list of jump instructions.

Table 4-5. Jump Instructions

4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data

transfer between the CPU and peripherals, and also data

transfers between peripherals. The PHUB and DMA also control

device configuration during boot. The PHUB consists of:

There are two PHUB masters: the CPU and the DMA controller.

Both masters may initiate transactions on the bus. The DMA

channels can handle peripheral communication without CPU

intervention. The arbiter in the central hub determines which

DMA channel is the highest priority if there are multiple requests.

Document Number: 001-11729 Rev. *R

ACALL addr11

LCALL addr16

RET

RETI

AJMP addr11

LJMP addr16

SJMP rel

JMP @A + DPTR

JZ rel

JNZ rel

CJNE A,Direct, rel

CJNE A, #data, rel

CJNE Rn, #data, rel

CJNE @Ri, #data, rel

DJNZ Rn,rel

DJNZ Direct, rel

NOP

A central hub that includes the DMA controller, arbiter, and

router

Multiple spokes that radiate outward from the hub to most

peripherals

Mnemonic

Absolute subroutine call

Long subroutine call

Return from subroutine

Return from interrupt

Absolute jump

Long jump

Short jump (relative address)

Jump indirect relative to DPTR

Jump if accumulator is zero

Jump if accumulator is nonzero

Compare direct byte to accumulator and jump if not equal

Compare immediate data to accumulator and jump if not equal

Compare immediate data to register and jump if not equal

Compare immediate data to indirect RAM and jump if not equal

Decrement register and jump if not zero

Decrement direct byte and jump if not zero

No operation

Description

4.4.1 PHUB Features

Table 4-6. PHUB Spokes and Peripherals

PHUB Spokes

CPU and DMA controller are both bus masters to the PHUB

Eight multi-layer AHB bus parallel access paths (spokes) for

peripheral access

Simultaneous CPU and DMA access to peripherals located on

different spokes

Simultaneous DMA source and destination burst transactions

on different spokes

Supports 8-, 16-, 24-, and 32-bit addressing and data

0

1

2

3

4

5

6

7

SRAM

IOs, PICU,

PHUB local configuration,

Clocks, IC, SWV, EEPROM,

programming interface

Analog interface and

USB, CAN,

DFB

UDBs group 1

UDBs group 2

PSoC

EMIF

I

®

2

C,

3: CY8C38 Family

Timers, Counters, and PWMs

Bytes

Peripherals

2

3

1

1

2

3

2

1

2

2

3

3

3

3

2

3

1

trim,

Power

Decimator

Data Sheet

Flash

Page 15 of 129

Cycles

manager,

4

4

4

4

3

4

3

5

4

4

5

4

4

5

4

5

1

Table 4-5

[+] Feedback