CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 30

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

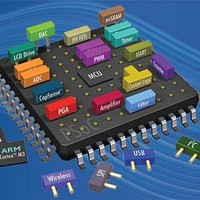

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in

Table 6-2

easily provide required functionality and processing power while

simultaneously minimizing power consumption and maximizing

battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power

consumption are:

Table 6-2. Power Modes

Table 6-3. Power Modes Wakeup Time and Power Consumption

Document Number: 001-11729 Rev. *R

Active

Alternate

Active

Sleep

Hibernate

Note

Power Modes

Active

Alternate

Active

Sleep

Hibernate <100 µs

13. Bus clock off. Execute from CPU instruction buffer at 6 MHz. See

Active

Alternate Active

Sleep

Hibernate

Modes

Sleep

and

<15 µs

Wakeup

–

–

Table

Time

Primary mode of operation, all

peripherals available

(programmable)

Similar to Active mode, and is

typically configured to have

fewer peripherals active to

reduce power. One possible

configuration is to use the UDBs

for processing, with the CPU

turned off

All subsystems automatically

disabled

All subsystems automatically

disabled

Lowest power consuming mode

with all peripherals and internal

regulators disabled, except

hibernate regulator is enabled

Configuration and memory

contents retained

6-3. The power modes allow a design to

200 nA

1.2 mA

–

1 µA

Description

Current

(typ)

[13]

Yes

User

defined

No

No

Execution

Code

Wakeup, reset,

manual register

entry

Manual register

entry

Manual register

entry

Manual register

entry

Entry Condition Wakeup Source

Resources

All

All

I

None

2

C

Digital

Table 11-2

on page 65.

All

All

Comparator ILO/kHzECO

None

Resources

Any interrupt

Any interrupt

Comparator,

PICU, I

CTW, LVD

PICU

Active is the main processing mode. Its functionality is

configurable. Each power controllable subsystem is enabled or

disabled by using separate power configuration template

registers. In alternate active mode, fewer subsystems are

enabled, reducing power. In sleep mode most resources are

disabled regardless of the template settings. Sleep mode is

optimized to provide timed sleep intervals and Real Time Clock

functionality. The lowest power mode is hibernate, which retains

register and SRAM state, but no clocks, and allows wakeup only

from I/O pins.

transitions between power modes

Analog

2

C, RTC,

All

None

Clock Sources

All

Figure 6-5

Available

Any

(programmable)

Any

(programmable)

ILO/kHzECO

Active Clocks

PSoC

on page 31 illustrates the allowable

Wakeup Sources

–

–

Comparator,

PICU, I

CTW, LVD

PICU

®

3: CY8C38 Family

All regulators available.

Digital and analog

regulators can be disabled

if external regulation used.

All regulators available.

Digital and analog

regulators can be disabled

if external regulation used.

Both digital and analog

regulators buzzed.

Digital and analog

regulators can be disabled

if external regulation used.

Only hibernate regulator

active.

2

C, RTC,

Data Sheet

Regulator

Page 30 of 129

All

All

XRES, LVD,

WDR

XRES

Sources

Reset

[+] Feedback