CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 39

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any

operating V

A common application for this feature is connection to a bus such

as I

voltages. In the I

Open Drain, Drives Low mode for the SIO pin. This allows an

external pull-up to pull the I

supply. For example, the PSoC chip could operate at 1.8 V, and

an external device could run from 5 V. Note that the SIO pin’s V

and V

pin. The I/O pin must be configured into a high impedance drive

mode, open drain low drive mode, or pull-down drive mode, for

over voltage tolerance to work properly. Absolute maximum

ratings for the device must be observed for all I/O pins.

6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High

Impedance Analog state. After reset is released, the state can be

reprogrammed on a port-by-port basis to pull-down or pull-up. To

ensure correct reset operation, the port reset configuration data

is stored in special nonvolatile registers. The stored reset data is

automatically transferred to the port reset configuration registers

at reset release.

6.4.17 Low-Power Functionality

In all low-power modes the I/O pins retain their state until the part

is awakened and changed or reset. To awaken the part, use a

pin interrupt, because the port interrupt logic continues to

function in all low-power modes.

6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality

in addition to their GPIO or SIO functionality. The specific special

function pins are listed in

are:

Document Number: 001-11729 Rev. *R

There are no current limitations for the SIO pins as they present a

high impedance load to the external circuit where Vddio < V

5.5 V.

The GPIO pins must be limited to 100 µA using a current limiting

resistor. GPIO pins clamp the pin voltage to approximately one

diode above the Vddio supply where Vddio < V

In case of a GPIO pin configured for analog input/output, the

analog voltage on the pin must not exceed the Vddio supply

voltage to which the GPIO belongs.

Digital

Analog

2

4- to 25-MHz crystal oscillator

32.768-kHz crystal oscillator

Wake from sleep on I

for I

JTAG interface pins

SWD interface pins

SWV interface pins

External reset

Opamp inputs and outputs

High current IDAC outputs

External reference inputs

C where different devices are running from different supply

IL

2

levels are determined by the associated Vddio supply

C if wake from sleep is not required.

DD

.

2

C case, the PSoC chip is configured into the

Pinouts

2

C address match. Any pin can be used

2

C bus voltage above the PSoC pin

on page 5. The special features

IN

< V

DDA

IN

.

<

IH

6.4.19 JTAG Boundary Scan

The device supports standard JTAG boundary scan chains on all

I/O pins for board level test.

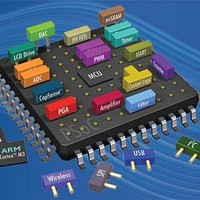

7. Digital Subsystem

The digital programmable system creates application specific

combinations of both standard and advanced digital peripherals

and custom logic functions. These peripherals and logic are then

interconnected to each other and to any pin on the device,

providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined

here to provide an overview of capabilities and architecture. You

do not need to interact directly with the programmable digital

system at the hardware and register level. PSoC Creator

provides a high level schematic capture graphical interface to

automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

Figure 7-1. CY8C38 Digital Programmable Architecture

UDB – These form the core functionality of the digital

programmable system. UDBs are a collection of uncommitted

logic (PLD) and structural logic (Datapath) optimized to create

all common embedded peripherals and customized

functionality that are application or design specific.

Universal digital block array – UDB blocks are arrayed within

a matrix of programmable interconnect. The UDB array

structure is homogeneous and allows for flexible mapping of

digital functions onto the array. The array supports extensive

and flexible routing interconnects between UDBs and the

Digital System Interconnect.

Digital system interconnect (DSI) – Digital signals from UDBs,

fixed function peripherals, I/O pins, interrupts, DMA, and other

system core signals are attached to the digital system

interconnect to implement full featured device connectivity. The

DSI allows any digital function to any pin or other feature

routability when used with the universal digital block array.

UDB

UDB

UDB

UDB

UDB

UDB

and Fixed Function Peripherals

and Fixed Function Peripherals

DSI Routing Interface

DSI Routing Interface

Digital Core System

Digital Core System

PSoC

UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

®

3: CY8C38 Family

UDB

UDB

UDB

UDB

UDB

UDB

Data Sheet

Page 39 of 129

[+] Feedback