CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 54

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

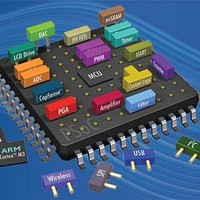

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

Analog local buses (abus) are routing resources located within

the analog subsystem and are used to route signals between

different analog blocks. There are eight abus routes in CY8C38,

four in the left half (abusl [0:3]) and four in the right half (abusr

[0:3]) as shown in

globals and analog mux buses from being used for

interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct

signals into and out of the analog blocks. A multiplexer can have

only one connection on at a time, whereas a switch can have

multiple connections on simultaneously. In

multiplexers are indicated by grayed ovals and switches are

indicated by transparent ovals.

8.2 Delta-sigma ADC

The CY8C38 device contains one delta-sigma ADC. This ADC

offers differential input, high resolution and excellent linearity,

making it a good ADC choice for both audio signal processing

and measurement applications. The converter's nominal

operation is 16 bits at 48 ksps. The ADC can be configured to

output 20-bit resolution at data rates of up to 187 sps. At a fixed

clock rate, resolution can be traded for faster data rates as

shown in

Table 8-1. Delta-sigma ADC Performance

Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

Document Number: 001-11729 Rev. *R

1000000

100000

10000

1000

100

10

Bits

1

20

16

12

6

8

Table 8-1

8

Continuous

Multi-Sample

Multi-SampleTurbo

Maximum Sample Rate

Figure

and

10

Figure

8-2. Using the abus saves the analog

(sps)

192 k

384 k

12

48 k

187

8-3.

Resolution, bits

14

16

Figure

SINAD (dB)

18

8-2,

84

66

43

–

20

22

8.2.1 Functional Description

The ADC connects and configures three basic components,

input buffer, delta-sigma modulator, and decimator. The basic

block diagram is shown in

muxes is delivered to the delta-sigma modulator either directly or

through the input buffer. The delta-sigma modulator performs the

actual analog to digital conversion. The modulator over-samples

the input and generates a serial data stream output. This high

speed data stream is not useful for most applications without

some type of post processing, and so is passed to the decimator

through the Analog Interface block. The decimator converts the

high speed serial data stream into parallel ADC results. The

modulator/decimator frequency response is [(sin x)/x]

frequency response is shown in

Figure 8-4. Delta-sigma ADC Block Diagram

Figure 8-5. Delta-sigma ADC Frequency Response,

Normalized to Output, Sample Rate = 48 kHz

Resolution and sample rate are controlled by the Decimator.

Data is pipelined in the decimator; the output is a function of the

last four samples. When the input multiplexer is switched, the

output data is not valid until after the fourth sample after the

switch.

8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four

modes: Single Sample, Multi Sample, Continous, or Multi

Sample (Turbo). All four modes are started by either a write to

the start bit in a control register or an assertion of the Start of

Conversion (SoC) signal. When the conversion is complete, a

status bit is set and the output signal End of Conversion (EoC)

asserts high and remains high until the value is read by either the

DMA controller or the CPU.

(Analog Routing)

Input Mux

Input Mux

Negative

Positive

-100

-10

-20

-30

-40

-50

-60

-70

-80

-90

0

100

1,000

PSoC

Buffer

Input

Figure

®

Input frequency, Hz

Input Frequency, Hz

Modulator

Figure

Sigma

10,000

3: CY8C38 Family

Delta

8-4. The signal from the input

8-5.

Decimator

Data Sheet

100,000

SOC

Page 54 of 129

4

; a typical

12 to 20 Bit

Result

EOC

1,000,000

[+] Feedback