LH7A404N0F092B3 Sharp Electronics, LH7A404N0F092B3 Datasheet

LH7A404N0F092B3

Specifications of LH7A404N0F092B3

Available stocks

Related parts for LH7A404N0F092B3

LH7A404N0F092B3 Summary of contents

Page 1

Product data sheet FEATURES • 32-bit ARM9TDMI™ RISC Core – Cache Instruction and 8 kB Data Cache – MMU (Windows CE™ Enabled) – 266 MHz; See Table 1 for speed options • ...

Page 2

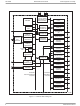

LH7A404 ARM 922T ASYNCHRONOUS MEMORY CONTROLLER PCMCIA/CF EXTERNAL BUS CONTROLLER INTERFACE SYNCHRONOUS MEMORY CONTROLLER LCD AHB BUS COLOR LCD CONTROLLER ADVANCED INTERFACE (ALI) USB HOST INTERFACE HIGH-PERFORMANCE 2 NXP Semiconductors 14.7456 MHz 32.768 kHz OSCILLATOR, PLL1 and PLL2, POWER MANAGEMENT, ...

Page 3

System-on-Chip LFBGA SIGNAL E10 E11 H10 H11 K5 K8 K13 K16 L5 VDD I/O Ring Power L8 L13 L16 N10 N11 T10 T11 U18 J9 J10 J11 J12 K9 K10 K11 K12 L9 VSS I/O Ring Ground L10 L11 ...

Page 4

LH7A404 Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL E6 E15 F5 F16 J16 VSSC Core Ground M5 R5 R16 T6 T15 Y17 VDDA Analog Power for PLL1 and PLL2 W17 V16 VSSA Analog Ground for PLL1 and PLL2 ...

Page 5

System-on-Chip Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL N19 D0 P20 D1 N18 D2 N20 D3 M16 D4 M18 D5 L18 D6 L17 D7 L19 D8 J19 D9 K17 D10 J18 D11 H19 D12 G20 D13 G19 ...

Page 6

LH7A404 Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL N17 A2/SA0 M19 A3/SA1 M20 A4/SA2 L20 A5/SA3 M17 A6/SA4 K18 A7/SA5 K20 A8/SA6 Asynchronous Address Bus and Synchronous Address Bus K19 A9/SA7 J20 A10/SA8 H20 A11/SA9 J17 A12/SA10 H18 ...

Page 7

System-on-Chip Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL C14 SCKE3 Clock Enable 3 for Synchronous Memory D14 SCLK Synchronous Memory Clock A13 nBLE0 Byte Lane Enable 0 U9 nBLE1 Byte Lane Enable 1 Y7 nBLE2 Byte Lane ...

Page 8

LH7A404 Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL V1 PC7 GPIO Port C7 Y11 PD0/LCDVD8 U10 PD1/LCDVD9 W12 PD2/LCDVD10 V11 PD3/LCDVD11 • GPIO Port D[7:0] • LCD Video Data Interface W11 PD4/LCDVD12 U11 PD5/LCDVD13 V12 PD6/LCDVD14 Y12 PD7/LCDVD15 ...

Page 9

System-on-Chip Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL • GPIO Port G2 Y3 PG2/nPCIOR • I/O Read Strobe for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode • GPIO Port G3 U5 PG3/nPCIOW • ...

Page 10

LH7A404 Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL • GPIO Port H7 PH7/ U7 • Status Read Enable for PC Card (PCMCIA or nPCSTATRE CompactFlash) in Single or Dual Card mode • LCD Frame Pulse T4 LCDFP/LCDSPS • ...

Page 11

System-on-Chip Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL • Audio Codec (AC97) Clock C7 ACBITCLK • Audio Codec (ACI) Clock • Audio Codec (AC97) Output B7 ACOUT • Audio Codec (ACI) Output • Audio Codec (AC97) Synchronization ...

Page 12

LH7A404 Table 2. LH7A404 Functional Pin List (Cont’d) LFBGA SIGNAL • ADC channel 3 U13 AN3/LR/Y- • Touch Screen Controller Lower Right • Touch Screen Controller Y-minus • ADC channel 4 V14 AN4/WIPER • Wiper input from 5-wire Touch Screen ...

Page 13

System-on-Chip LFBGA RESET LCD PIN STATE SIGNAL SINGLE PANEL L4 PA1 LCDVD17 M2 PA0 LCDVD16 Y12 PD7 LCDVD15 V12 PD6 LCDVD14 U11 PD5 LCDVD13 W11 PD4 LCDVD12 V11 PD3 LCDVD11 W12 PD2 LCDVD10 U10 PD1 LCDVD9 Y11 PD0 LCDVD8 ...

Page 14

LH7A404 Table 5. LFBGA Numerical Pin List LFBGA SIGNAL A1 PE7/SCDATEN 95 mV/ns A2 DACK1 95 mV/ns A3 DREQ0 A4 MMCDATA2 110 mV/ns A5 MMCCLK 110 mV/ns A6 ACSYNC 110 mV/ns A7 PF6/INT6/PCRDY1 110 mV/ns A8 PF2/INT2 110 mV/ns A9 ...

Page 15

System-on-Chip Table 5. LFBGA Numerical Pin List (Cont’d) LFBGA SIGNAL E11 VDD E12 SCIO 95 mV/ns E13 DQM1 95 mV/ns E14 VDDC E15 VSSC E16 nSCS3 95 mV/ns E17 A21 95 mV/ns E18 D20 95 mV/ns E19 D18 95 ...

Page 16

LH7A404 Table 5. LFBGA Numerical Pin List (Cont’d) LFBGA SIGNAL M3 PA2 110 mV/ns M4 PA3 110 mV/ns M5 VSSC M9 VSS M10 VSS M11 VSS M12 VSS M16 D4 95 mV/ns M17 A6/SA4 95 mV/ns M18 D5 95 mV/ns ...

Page 17

System-on-Chip Table 5. LFBGA Numerical Pin List (Cont’d) LFBGA SIGNAL V6 PH0/PCRESET1 110 mV/ns V7 PH6/nAC97RESET 110 mV/ns V8 LCDVD0 95 mV/ns V9 LCDENAB/LCDM 95 mV/ns V10 PE2/LCDVD6 95 mV/ns V11 PD3/LCDVD11 95 mV/ns V12 PD6/LCDVD14 95 mV/ns V13 ...

Page 18

LH7A404 ROM FLASH SRAM SDRAM COMPACT FLASH PC PCMCIA CARD DEVICE HOST SYSTEM DESCRIPTIONS ARM922T Processor The LH7A404 microcontroller features the ARM922T cached core with an Advanced High-performance Bus (AHB) interface. The processor is a member of the ARM9T family ...

Page 19

System-on-Chip Power Modes The LH7A404 has three operational states: Run, Halt, and Standby. During Run all clocks are hardware enabled and the processor is clocked. In the Halt mode the device is functioning, but the processor clock is halted ...

Page 20

LH7A404 AMBA APB BUS The AMBA APB provides a lower-bandwidth bus for peripherals accessed less frequently. This reduces the loading on the AHB, allowing it to run faster to maxi- mize system performance, while the APB can operate at a ...

Page 21

System-on-Chip BOOT DEVICE External device 8-bit interface, 3-byte address NAND Flash 8-bit interface, 4-byte address NAND Flash 8-bit interface, 5-byte address NAND Flash 16-bit interface, 3-byte address NAND Flash 16-bit interface, 4-byte address NAND Flash 16-bit interface, 5-byte address ...

Page 22

LH7A404 Vectored Interrupt Controller (VIC) The LH7A404 has two VICs working together to manage interrupt requests from on-chip and off-chip sources. Each VIC performs these primary functions: • Determine if an interrupt source is disabled or can generate an FIQ ...

Page 23

System-on-Chip Embedded SRAM The LH7A404 incorporates embedded SRAM. This embedded memory is used for storing code, data, or LCD frame data and is contiguous with external SDRAM. The large enough to store a ...

Page 24

LH7A404 SD/MMC INTERFACE DESCRIPTION The SD/MMC controller uses the three-wire signal bus (clock, command, and data) to input and output data to and from the MMC, and to configure and acquire status information from the card. The SD con- troller ...

Page 25

System-on-Chip The DMA Controller features: • Two dedicated channels for M2M and external M2P/P2M • Ten fully independent, programmable DMA control- ler internal M2P/P2M channels (5 Tx and 5 Rx) • Channels assignable to one of a number of ...

Page 26

LH7A404 Color LCD Controller The LH7A404’s LCD Controller is programmable to support up to 1,024 × 768, 16-bit color LCD panels. It interfaces directly to STN, color STN, TFT, AD-TFT, and HR-TFT panels. Unlike other LCD controllers, the LH7A404’s LCD ...

Page 27

System-on-Chip UART/IrDA The LH7A404 contains three UARTs; UART1, UART2, and UART3. The UART performs: • Serial-to-Parallel conversion on data received from the peripheral device • Parallel-to-Serial conversion on data transmitted to the peripheral device. The transmit and receive paths ...

Page 28

LH7A404 • Battery voltage sense in addition to normal direct voltage inputs • A 9-channel multiplexer for routing user-selected inputs to A/D • × 16 FIFO for 10-bit digital output of A/D • A pen-down sensor to generate ...

Page 29

System-on-Chip ELECTRICAL SPECIFICATIONS IMPORTANT: The LH7A404 is an electrostatic discharge (ESD) sensitive device. ESD protection circuitry internal to the LH7A404 has been added to reduce ESD susceptibility. Appropriate ESD precautions are still required during handling to prevent degradation or ...

Page 30

LH7A404 Recommended Operating Conditions for LH7A404-N0E-092-xx/LH7A404-N0F-092-xx PARAMETER DC Core Supply Voltage (VDDC) DC I/O Supply Voltage (VDD) DC Analog Supply Voltage (VDDA) DC A/D and TSC Supply Voltage (VDDAD) Clock Frequency Bus Clock Frequency External Clock Input (XTALIN) External Clock ...

Page 31

System-on-Chip Power Supply Sequencing NXP recommends that the 1.8 V power supply be energized before the 3.3 V supply. If this is not possi- ble, the 1.8 V supply may not lag the 3.3 V supply by more than ...

Page 32

LH7A404 Analog-To-Digital Converter Electrical Characteristics Table 9 shows the derated specifications for extended temperature operation. See Figure 6 for the ADC transfer characteristics. Table 9. ADC Electrical Characteristics PARAMETER A/D Resolution Throughput Conversion Acquisition Time Data Format Clk Frequency Differential ...

Page 33

System-on-Chip 1024 1023 1022 1021 1020 1019 1018 9 8 CENTER OF A STEP OF THE ACTUAL 7 TRANSFER CURVE LSB OFFSET ERROR DNL AC Test Conditions PARAMETER DC I/O ...

Page 34

LH7A404 CURRENT CONSUMPTION BY OPERATING MODE Current consumption can depend on a number of parameters. To make these data more usable, the values presented in Table 11 were derived under the conditions described here. Maximum Specified Value The values specified ...

Page 35

System-on-Chip AC Specifications All signals described in Table 12 relate to transi- tions following an internal reference clock signal. The illustration in Figure 7 represents all cases of these sets of measurement parameters. The reference clock signals in this ...

Page 36

LH7A404 SIGNAL TYPE LOAD SYMBOL ASYNCHRONOUS MEMORY INTERFACE SIGNALS (+ [wait states × HCLK period]) Output 50 pF tRC A[27:0] Output 50 pF tWC — — tWS tDVWE tDHWE Output 50 pF tDVBE tDHBE tDSCS D[31:0] tDHCS tDSOE Input — ...

Page 37

System-on-Chip Table 12. AC Signal Characteristics (Cont’d) SIGNAL TYPE LOAD SYMBOL tOVD Output 50 pF tOHD D[31:0] tISD Input — tIHD tOVCE1 nPCCE1 Output 50 pF tOHCE1 tOVCE2 nPCCE2 Output 50 pF tOHCE2 tOVOE nPCOE Output 50 pF tOHOE ...

Page 38

LH7A404 SMC Waveforms Figure 8 and Figure 9 show waveforms and timing for an external asynchronous memory Write. Figure 10 and Figure 11 show the waveforms and timing for an external asynchronous memory Read. 0 HCLK A[27:0] D[31:0] nCSx nWE ...

Page 39

System-on-Chip 0 1 HCLK A[27:0] D[31:0] nCSx nWE nBLE 0 WAIT STATE Figure 9. External Asynchronous Memory Write, Four Wait States (BCRx:WST1 = 0b100) Product data sheet NXP Semiconductors VALID ADDRESS VALID DATA nCSx ...

Page 40

LH7A404 0 HCLK A[27:0] D[31:0] nCSx nOE nBLE Figure 10. External Asynchronous Memory Read, Zero Wait States (BCRx:WST1 = 0b000) 40 NXP Semiconductors tRC tAHOE, tAHBE VALID ADDRESS VALID DATA tDSCS tAVCS tCS nCS Valid tDSOE tAVOE ...

Page 41

System-on-Chip 0 1 HCLK A[27:0] nCS[3:0, CS[7:6] nOE nBLE D[31:0] 0 WAIT STATE, DATA WOULD BE LATCHED HERE Figure 11. External Asynchronous Memory Read, Four Wait States (BCRx:WST1 = 0b100) Product data sheet NXP Semiconductors ...

Page 42

LH7A404 TIMING FOR nWAIT SIGNALLING In addition to being able to program the number of Wait States, the SMC also can use nWAIT signalling to extend transactions. When the nWAIT input is asserted, the current transaction is held in suspense ...

Page 43

System-on-Chip tDA_nCS(x)_nWAIT nCS(x) nOE nWAIT SI SI SQ-4 HCLK Transaction WSD-4 WSD-3 WSD-2 Sequence DELAY DELAY DELAY NOTES: SQ: nWAIT Sampled and Queued SI: nWAIT Sampled and Ignored Figure 13. nWAIT Read Sequence (BCRx:WST1 = 4); Ignored and Queued ...

Page 44

LH7A404 tDA_nCS(x)_nWAIT nCS(x) nWE nWAIT SQ-4 SQ-3 HCLK Transaction WSD-2 WSD-1 Sequence DELAY DELAY NOTES: SQ: nWAIT Sampled and Queued SI: nWAIT Sampled and Ignored Figure 15. nWAIT Write Sequence (BCRx:WST1 = 2); Minimum Wait State Example PARAMETER tIDA_nCS(x)_nWAIT Delay ...

Page 45

System-on-Chip tDA_nCS(x)_nWAIT nCS(x) nWE nWAIT SI SI SQ-4 HCLK Transaction WSD-4 WSD-3 WSD2 Sequence DELAY DELAY DELAY NOTES: SQ: nWAIT Sampled and Queued SI: nWAIT Sampled and Ignored Figure 16. nWAIT Write Sequence (BCRx:WST1 = 4); Ignored and Queued ...

Page 46

LH7A404 tDA_nCS(x)_nWAIT nCS(x) nWE nWAIT HCLK WSD-4 Transaction Sequence DELAY NOTES: SQ: nWAIT Sampled and Queued SI: nWAIT Sampled and Ignored Figure 17. nWAIT Write Sequence (BCRx:WST1 = 4); nWAIT Has No Effect On Current Transaction 46 NXP Semiconductors tA_nWAIT ...

Page 47

System-on-Chip Synchronous Memory Controller Waveforms Figure 18 shows the waveform and timing for a Syn- chronous Burst Read (page already open). Figure 19 shows the waveform and timing for synchronous mem- ory to activate a bank and Write. SCLK ...

Page 48

LH7A404 SSP Waveforms The Synchronous Serial Port (SSP) supports three data frame formats: • Texas Instruments SSI • Motorola SPI • National Semiconductor MICROWIRE Each frame format is between 4 and 16 bits in length, depending upon the programmed data ...

Page 49

System-on-Chip For Motorola SPI, the serial frame pin (SSPFRM) is active LOW. The SPO and SPH bits in SSP Control Register 0 determine SSPCLK and SSPFRM operation SSPCLK nSSPFRM SSPRXD MSB MSB SSPTXD NOTE undefined. Figure 22. ...

Page 50

LH7A404 SSPCLK nSSPFRM SSPTXD/ SSSRXD Figure 25. Motorola SPI Frame Format (Continuous Transfer) with SPO = 0 and SPH = 1 SSPCLK nSSPFRM SSPTXD/ SSSRXD Figure 26. Motorola SPI Frame Format (Continuous Transfer) with SPO = 1 and SPH = ...

Page 51

System-on-Chip SSPCLK nSSPFRM SSPTXD/ LSB SSPRXD Figure 28. Motorola SPI Frame Format (Continuous Transfer) with SPO = 1 and SPH = 0 SSPCLK nSSPFRM SSPRXD Q MSB SSPTXD MSB NOTE undefined. Figure 29. Motorola SPI Frame Format ...

Page 52

LH7A404 For National Semiconductor MICROWIRE format, the serial frame pin (SSPFRM) is active LOW. Both the SSP and external slave device drive their output data on the falling edge of the clock, and latch data from the other device on ...

Page 53

System-on-Chip SSPCLK (Programmable CLOCK phase) SSPTX SSPRX SSPFRM (Programmable FRAME phase and duration) Product data sheet NXP Semiconductors tCLK CLOCK CLOCK PHASE 1 PHASE 2 tOVTX tOHTX BITn BITn-1 OUTPUT OUTPUT tISRX tIHRX BITn BITn-1 INPUT INPUT tOHFRM tOVFRM ...

Page 54

LH7A404 PC Card (PCMCIA) Waveforms Figure 33 shows the waveforms for PCMCIA Read transactions and Figure 34 shows the waveforms and timing for Write transactions. Figure 35 shows the pre- charge, access, and hold timing relationships. HCLK A[25:0] nPCREG nPCCEx ...

Page 55

System-on-Chip HCLK A[25:0] nPCREG nPCCEx (See Note 2) PCDIR D[15:0] nPCWE/ nPCIOW NOTES: 1. Precharge time, access time, and hold time are programmable wait-state times. 2. nPCCE1 nPCCE2 TRANSFER TYPE 0 0 Common Memory 0 1 Attribute Memory 1 ...

Page 56

LH7A404 MMC Interface Waveforms Figure 36 shows the waveforms and timing for an MMC command or data Write. Figure 37 shows the wave- forms and timing for an MMC command or data Read. MMCCLK MMCCMD MMCDATA MMCCLK MMCCMD MMCDATA ACBITCLK ...

Page 57

System-on-Chip Audio Codec Interface (ACI) Timing The timing for the Audio Codec Interface are shown in Figure 39 and Figure 40. Transmit data is clocked on the rising edge of ACBITCLK (whether transmitted by the LH7A404 ACI or by ...

Page 58

LH7A404 58 NXP Semiconductors Figure 42. STN Horizontal Timing 32-Bit System-on-Chip Product data sheet ...

Page 59

System-on-Chip Product data sheet NXP Semiconductors Figure 43. STN Vertical Timing LH7A404 59 ...

Page 60

LH7A404 60 NXP Semiconductors Figure 44. TFT Horizontal Timing 32-Bit System-on-Chip Product data sheet ...

Page 61

System-on-Chip Product data sheet NXP Semiconductors Figure 45. TFT Vertical Timing LH7A404 61 ...

Page 62

LH7A404 CLCDC CLOCK (INTERNAL) PERIPHCLKSEL2:LCSRC PERIPHCLKCTRL2:LCDCLK LCDCLKPRESCALE:LCDPSVAL (SHOWN FOR REFERENCE) LCDLP (HORIZONTAL SYNC PULSE) LCDDCLK (PANEL DATA CLOCK) TIMING2:PCD TIMING2:BCD TIMING2:IPC TIMING2:CPL LCDVD[17:0] 16 × (TIMING0:PPL+1) LCDENAB (INTERNAL DATA ENABLE) Y10 LCDDCLK (DELAYED FOR HR-TFT) LCDVD[17:0] (DELAYED FOR HR-TFT) LCDSPL ...

Page 63

System-on-Chip Clock and State Controller (CSC) Waveforms Figure 48 shows the behavior of the LH7A404 when coming out of Reset or Power-On. Table 13 gives the timing parameters. At Power-On, nPOR must be held LOW until the 32.768 kHz ...

Page 64

LH7A404 tDA_nPOR_CLKEN tDA_nPOR_nRSTO nPOR TRIGGER POINT WAKEUP nRESETOUT CLKEN Figure 49. nRESETOUT Timing for nPOR Trigger Table 14. nRESETOUT Timing Values for nPOR Trigger SIGNAL MIN. tDA_nPOR_nRSTO tDD_nPOR_nRSTO tDD_nPOR_WKUP 2 tA_WKUP 4 tDA_nPOR_CLKEN tDA_WKUP_CLKEN 2 add some timing margin to ...

Page 65

System-on-Chip tA_nURESET tDA_nURESET_CLKEN tDA_nURESET_nRSTO nURESET TRIGGER POINT WAKEUP nRESETOUT CLKEN Figure 50. nRESETOUT Timing for nURESET Trigger Table 15. nRESETOUT Timing Values for nURESET Trigger SIGNAL MIN. TYP. tDA_nURESET_nRSTO 2 tDD_nURESET_nRSTO 0 tA_nURESET 4 tDD_nURESET_WKUP 2 tA_WKUP 4 tDA_nURESET_CLKEN ...

Page 66

LH7A404 tDA_nPWRFL_CLKEN tDA_nPWRFL_nRSTO nPWRFL TRIGGER POINT WAKEUP nRESETOUT CLKEN Figure 51. nRESETOUT Timing for nPWRFL Trigger Table 16. nRESETOUT Timing Values for nPWRFL Trigger SIGNAL MIN. TYP. tDA_nPWRFL_nRSTO 2 tA_nRSTO 2 tA_nPWRFL 4 tDD_nPWRFL_WKUP 2 tA_WKUP 4 tDA_nPWRFL_CLKEN 2 tDA_WKUP_CLKEN ...

Page 67

System-on-Chip Reference Oscillator Circuit Design Figure 52 and Figure 53 show a reference oscillator design for both the 32.768 kHz and 14.7456 MHz clocks. Low Operating Temperatures and Noise Immunity The junction temperature, Tj, is the operating tem- perature ...

Page 68

LH7A404 INTERNAL TO THE LH7A404 EXTERNAL TO THE LH7A404 NOTES parallel-resonant type crystal. (See table) 2. The nominal values for C1 and C2 shown are for a crystal specified load capacitance (CL). 3. ...

Page 69

System-on-Chip Printed Circuit Board Layout Practices LH7A404 POWER SUPPLY DECOUPLING The LH7A404 has separate power and ground pins for different internal circuitry sections. The VDD and VSS pins supply power to I/O buffers, while VDDC and VSSC supply power ...

Page 70

LH7A404 PACKAGE SPECIFICATIONS LFBGA324: plastic low profile fine-pitch ball grid array package; 324 balls ball A1 index area ball ...

Page 71

System-on-Chip REVISION HISTORY Document ID Release date Data sheet status LH7A404_N_2 20080307 Product data sheet Modifications: • Changed status from ‘Preliminary’ to ‘Product’ • Fig. 19; replaced with correct figure. • Fig. 20; added timing symbols. LH7A404_N_1 20070716 Preliminary ...

Page 72

LH7A404 1. Legal information 1.1 Data sheet status [1][2] Document status Product status Objective [short] data sheet Development Preliminary [short] data sheet Qualification Product [short] data sheet Production [1] Please consult the most recently issued document before initiating or completing ...

Page 73

Dear customer from June 1 , 2007 NXP Semiconductors has acquired the LH7xxx ARM Microcontrollers from Sharp Microelectronics. The following changes are applicable to the attached data sheet. In data sheets where the previous Sharp or Sharp Corporation ...

Page 74

ANNEX A: Disclaimers (11) 1. t001dis100.fm: General (DS, AN, UM) General — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied the accuracy ...

Page 75

No offer to sell or license (DS) No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance ...