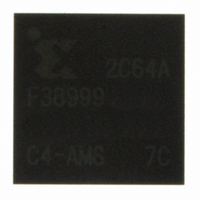

XC2C64A-7CPG56C Xilinx Inc, XC2C64A-7CPG56C Datasheet - Page 12

XC2C64A-7CPG56C

Manufacturer Part Number

XC2C64A-7CPG56C

Description

IC CR-II CPLD 64MCELL 56-BGA

Manufacturer

Xilinx Inc

Series

CoolRunner IIr

Specifications of XC2C64A-7CPG56C

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

6.7ns

Voltage Supply - Internal

1.7 V ~ 1.9 V

Number Of Logic Elements/blocks

4

Number Of Macrocells

64

Number Of Gates

1500

Number Of I /o

45

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-CSBGA

Features

Programmable

Voltage

1.8V

Memory Type

CMOS

For Use With

122-1536 - KIT STARTER SPARTAN-3E122-1532 - KIT DEVELOPMENT SPARTAN 3ADSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Logic Elements/cells

-

Other names

122-1408

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC2C64A-7CPG56C

Manufacturer:

XILINX

Quantity:

332

Part Number:

XC2C64A-7CPG56C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

CoolRunner-II CPLD Family

Programming

The programming data sequence is delivered to the device

using either Xilinx iMPACT software and a Xilinx download

cable,

JTAG-compatible board tester, or a simple microprocessor

interface that emulates the JTAG instruction sequence. The

iMPACT software also outputs serial vector format (SVF)

files for use with any tools that accept SVF format, including

automatic test equipment. See

Application Notes

In System Programming

All CoolRunner-II CPLD parts are 1.8V in system program-

mable. This means they derive their programming voltage

and currents from the 1.8V V

pins on the part. The V

operation, as they might assume another voltage ranging as

high as 3.3V down to 1.5V (however, all V

V

be programmed, and operate correctly). A 1.8V V

required to properly operate the internal state machines and

charge pumps that reside within the CPLD to do the nonvol-

atile programming operations. I/O pins are not in user mode

during JTAG programming; they are held in 3-state with a

weak pullup. The JTAG interface buffers are powered by a

dedicated power pin, V

other supply pins. V

ware is provided to deliver the bitstream to the CPLD and

drive the appropriate IEEE 1532 protocol. To that end, there

is a set of IEEE 1532 commands that are supported in the

CoolRunner-II CPLD parts. Programming times are less

than one second for 32 to 256 macrocell parts. Program-

ming times are less than four seconds for 384 and 512 mac-

rocell parts. Programming of CoolRunner-II CPLDs is only

guaranteed when operating in the commercial temperature

and voltage ranges as defined in the device-specific data

sheets.

On-The-Fly Reconfiguration (OTF)

The Xilinx ISE 5.2i tool supports OTF for CoolRunner-II

CPLDs. This permits programming a new nonvolatile pat-

tern into the part while another pattern is currently in use.

OTF has the same voltage and temperature specifications

as system programming. During pattern transition I/O pins

are in high impedance with a weak pullup to V

tion time typically lasts between 50 and 300 μs, depending

on density. See

JTAG Instructions

Table 7

same commands can be used by third party ATE products,

12

CCAUX

, and GND pins must be connected for the device to

a

shows the commands available to users. These

third-party

XAPP388

for more information on how to program.

CCAUX

CCAUX

CCIO

JTAG

for more information.

must be connected. Xilinx soft-

pins do not participate in this

, which is independent of all

CC

development

(internal supply voltage)

CoolRunner-II CPLD

CCIO

CCIO

system,

, V

. Transi-

CCINT

www.xilinx.com

CC

is

a

,

as well. The internal controllers can operate as fast as

66 MHz.

Table 7: JTAG Instructions

Power-Up Characteristics

CoolRunner-II CPLD parts must operate under the

demands of both the high-speed and the portable market

places; therefore, they must support hot plugging for the

high-speed world and tolerate most any power sequence to

its various voltage pins. They must also not draw excessive

current during power-up initialization. To those ends, the

general behavior is summarized as follows:

1. I/O pins are disabled until the end of power-up.

2. As supply rises, configuration bits transfer from

3. As power up completes, the outputs become as

4. For specific configuration times and power up

CoolRunner-II CPLD I/O pins are well behaved under all

operating conditions. During power-up, CoolRunner-II

devices employ internal circuitry which keeps the devices in

the quiescent state until the V

safe level (approximately 1.3V). In the quiescent state,

JTAG pins are disabled, and all device outputs are disabled

with the pins weakly pulled High, as shown in

the supply voltage reaches a safe level, all user registers

become initialized, and the device is immediately available

for operation, as shown in

obtained with a smooth V

V

If the device is in the erased state (before any user pattern

is programmed), the device outputs remain disabled with a

weak pull-up. The JTAG pins are enabled to allow the device

00000000

00000011

11111111

00000010

00000001

11111101 USERCODE Read USERCODE

11111100

11111010

CC

Code

nonvolatile memory to SRAM cells.

configured (input, output, or I/O).

requirements, see XAPP389.

value should occur within 1 second.

Instruction

PRELOAD

EXTEST

BYPASS

IDCODE

INTEST

CLAMP

HIGHZ

CC

Force boundary scan data onto

outputs

Latch macrocell data into

boundary scan cells

Insert bypass register between

TDI and TDO

Force boundary scan data onto

inputs and feedbacks

Read IDCODE

Force output into high

impedance state

Latch present output state

DS090 (v3.1) September 11, 2008

Figure

rise in less than 4 ms. Final

CCINT

supply voltage is at a

Description

12. Best results are

Product Specification

Table

8. When

R