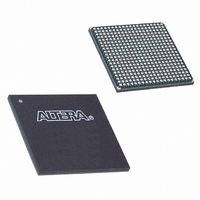

EP1C4F400C8N Altera, EP1C4F400C8N Datasheet - Page 36

EP1C4F400C8N

Manufacturer Part Number

EP1C4F400C8N

Description

IC CYCLONE FPGA 4K LE 400-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C4F400C8N

Number Of Logic Elements/cells

4000

Number Of Labs/clbs

400

Total Ram Bits

78336

Number Of I /o

301

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

400-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1806

EP1C4F400C8N

EP1C4F400C8N

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C4F400C8N

Manufacturer:

CYCLONE

Quantity:

5 510

Company:

Part Number:

EP1C4F400C8N

Manufacturer:

ALTERA

Quantity:

104

Part Number:

EP1C4F400C8N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP1C4F400C8NAA

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP1C4F400C8NAB

Manufacturer:

ALTERA

Quantity:

3 000

Cyclone Device Handbook, Volume 1

Figure 2–22. Global Clock Generation

Notes to

(1)

(2)

(3)

2–30

Preliminary

CLK1 (3)

DPCLK1

DPCLK0

CLK0

The EP1C3 device in the 100-pin TQFP package has five DPCLK pins (DPCLK2, DPCLK3, DPCLK4, DPCLK6, and

DPCLK7).

EP1C3 devices only contain one PLL (PLL 1).

The EP1C3 device in the 100-pin TQFP package does not have dedicated clock pins CLK1 and CLK3.

Figure

2–22:

Cyclone Device

PLL1

The eight global clock lines in the global clock network drive throughout

the entire device. The global clock network can provide clocks for all

resources within the device—IOEs, LEs, and memory blocks. The global

clock lines can also be used for control signals, such as clock enables and

synchronous or asynchronous clears fed from the external pin, or DQS

signals for DDR SDRAM or FCRAM interfaces. Internal logic can also

drive the global clock network for internally generated global clocks and

asynchronous clears, clock enables, or other control signals with large

fanout.

network.

2

DPCLK2

DPCLK7

Figure 2–22

From logic

array

Note (1)

4

4

shows the various sources that drive the global clock

8

4

From logic

DPCLK6

array

4

DPCLK3

Global Clock

Network

2

PLL2

(2)

Altera Corporation

May 2008

DPCLK4

CLK2

CLK3 (3)

DPCLK5