EP2S90F1508I4 Altera, EP2S90F1508I4 Datasheet - Page 65

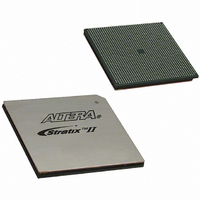

EP2S90F1508I4

Manufacturer Part Number

EP2S90F1508I4

Description

IC STRATIX II FPGA 90K 1508-FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S90F1508I4

Number Of Logic Elements/cells

90960

Number Of Labs/clbs

4548

Total Ram Bits

4520488

Number Of I /o

902

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

1508-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1923

EP2S90F1508I4

EP2S90F1508I4

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2S90F1508I4

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP2S90F1508I4N

Manufacturer:

ALTERA

Quantity:

586

Altera Corporation

May 2007

The Stratix II clock networks can be disabled (powered down) by both

static and dynamic approaches. When a clock net is powered down, all

the logic fed by the clock net is in an off-state thereby reducing the overall

power consumption of the device.

The global and regional clock networks can be powered down statically

through a setting in the configuration (.sof or .pof) file. Clock networks

that are not used are automatically powered down through configuration

bit settings in the configuration file generated by the Quartus II software.

The dynamic clock enable/disable feature allows the internal logic to

control power up/down synchronously on GCLK and RCLK nets and

PLL_OUT pins. This function is independent of the PLL and is applied

directly on the clock network or PLL_OUT pin, as shown in

through 2–39.

1

Enhanced & Fast PLLs

Stratix II devices provide robust clock management and synthesis using

up to four enhanced PLLs and eight fast PLLs. These PLLs increase

performance and provide advanced clock interfacing and clock-

frequency synthesis. With features such as clock switchover,

spread-spectrum clocking, reconfigurable bandwidth, phase control, and

reconfigurable phase shifting, the Stratix II device’s enhanced PLLs

provide you with complete control of clocks and system timing. The fast

PLLs provide general purpose clocking with multiplication and phase

shifting as well as high-speed outputs for high-speed differential I/O

support. Enhanced and fast PLLs work together with the Stratix II

high-speed I/O and advanced clock architecture to provide significant

improvements in system performance and bandwidth.

The following restrictions for the input clock pins apply:

•

•

•

•

In general, even CLK numbers connect to the inclk[0] port of

CLKCTRL, and odd CLK numbers connect to the inclk[1] port

of CLKCTRL.

Failure to comply with these restrictions will result in a no-fit

error.

CLK0 pin -> inclk[0] of CLKCTRL

CLK1 pin -> inclk[1] of CLKCTRL

CLK2 pin -> inclk[0] of CLKCTRL

CLK3 pin -> inclk[1] of CLKCTRL

Stratix II Device Handbook, Volume 1

Stratix II Architecture

Figures 2–37

2–57