XCS30XL-4VQ100I Xilinx Inc, XCS30XL-4VQ100I Datasheet - Page 13

XCS30XL-4VQ100I

Manufacturer Part Number

XCS30XL-4VQ100I

Description

IC FPGA 3.3V I-TEMP HP 100VQFP

Manufacturer

Xilinx Inc

Series

Spartan™-XLr

Datasheet

1.XCS05XL-4VQG100C.pdf

(83 pages)

Specifications of XCS30XL-4VQ100I

Number Of Logic Elements/cells

1368

Number Of Labs/clbs

576

Total Ram Bits

18432

Number Of I /o

77

Number Of Gates

30000

Voltage - Supply

3 V ~ 3.6 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

100-TQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XCS30XL-4VQ100I

Manufacturer:

XILINX

Quantity:

440

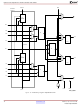

The four Primary Global buffers offer the shortest delay and

negligible skew. Four Secondary Global buffers have

slightly longer delay and slightly more skew due to poten-

tially heavier loading, but offer greater flexibility when used

to drive non-clock CLB inputs. The eight Global Low-Skew

buffers in the Spartan-XL devices combine short delay, neg-

ligible skew, and flexibility.

The Primary Global buffers must be driven by the semi-ded-

icated pads (PGCK1-4). The Secondary Global buffers can

be sourced by either semi-dedicated pads (SGCK1-4) or

internal nets. Each corner of the device has one Primary

buffer and one Secondary buffer. The Spartan-XL family

has eight global low-skew buffers, two in each corner. All

can be sourced by either semi-dedicated pads (GCK1-8) or

internal nets.

Using the library symbol called BUFG results in the software

choosing the appropriate clock buffer, based on the timing

requirements of the design. A global buffer should be spec-

ified for all timing-sensitive global signal distribution. To use

a global buffer, place a BUFGP (primary buffer), BUFGS

(secondary buffer), BUFGLS (Spartan-XL family global

low-skew buffer), or BUFG (any buffer type) element in a

schematic or in HDL code.

DS060 (v1.8) June 26, 2008

Product Specification

BUFGP

BUFGS

IOB

IOB

PGCK1

SGCK2

R

locals

locals

SGCK1

PGCK2

4

BUFGP

BUFGS

X4

One BUFGP

per Global Line

Any BUFGS

Figure 11: 5V Spartan Family Global Net Distribution

IOB

IOB

locals

locals

X4

IOB

IOB

4

www.xilinx.com

CLB

CLB

CLB

CLB

Advanced Features Description

Distributed RAM

Optional modes for each CLB allow the function generators

(F-LUT and G-LUT) to be used as Random Access Memory

(RAM).

Read and write operations are significantly faster for this

on-chip RAM than for off-chip implementations. This speed

advantage is due to the relatively short signal propagation

delays within the FPGA.

Memory Configuration Overview

There are two available memory configuration modes: sin-

gle-port RAM and dual-port RAM. For both these modes,

write operations are synchronous (edge-triggered), while

read operations are asynchronous. In the single-port mode,

a single CLB can be configured as either a 16 x 1, (16 x 1)

x 2, or 32 x 1 RAM array. In the dual-port mode, a single

CLB can be configured only as one 16 x 1 RAM array. The

different CLB memory configurations are summarized in

Table

grammed into a Spartan/XL FPGA CLB.

Table 8: CLB Memory Configurations

Single-Port

Dual-Port

Spartan and Spartan-XL FPGA Families Data Sheet

8. Any of these possibilities can be individually pro-

Mode

IOB

IOB

4

locals

locals

X4

IOB

IOB

Any BUFGS

One BUFGP

per Global Line

16 x 1

√

√

(16 x 1) x 2

X4

BUFGS

BUFGP

√

−

4

SGCK3

PGCK4

locals

locals

SGCK4

PGCK3

ds060_11_080400

32 x 1

√

−

BUFGS

IOB

IOB

BUFGP

13