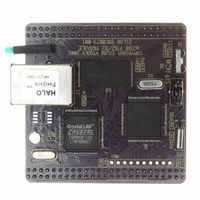

EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet

EZ80F920120MOD

Specifications of EZ80F920120MOD

EZ80F920120MOD

Related parts for EZ80F920120MOD

EZ80F920120MOD Summary of contents

Page 1

... Flash Microcontrollers eZ80F92/eZ80F93 Product Specification PRELIMINARY PS015308-0404 ZiLOG Worldwide Headquarters • 532 Race Street • San Jose, CA 95126 Telephone: 408.558.8500 • Fax: 408.558.8300 • www.ZiLOG.com ...

Page 2

... T elephone: 408.558.8500 Fax: 408.558.8300 www .zilog.com ZiLOG gistered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which the y are associated. Document Disclaimer © 2004 by ZiLOG, Inc. All rights reserv ed. Information in this publication concerning the de vices, applications, or technology described is intended to suggest possible uses and may be superseded ...

Page 3

T able of Contents L ist of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4

Bus Mode Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5

... C General Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142 Transferring Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144 Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154 ZiLOG Debug Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163 ZDI-Supported Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164 ZDI Clock and Data Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164 ZDI Start Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165 ZDI Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166 ZDI Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167 ZDI Read Operations ...

Page 6

... Wait State Timing for Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240 General Purpose I/O Port Input Sample Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 241 External Bus Acknowledge Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242 External System Clock Driver (PHI) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242 ZiLOG Debug Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243 Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245 Part Number Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245 Precharacterization Product ...

Page 7

List of Figures Figure 1. eZ80F92 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 8

Figure 35. ICC Versus Frequency in HALT Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 232 Figure 36. ICC Versus ...

Page 9

List of Tables Table 1. Clock Peripheral Power-Down Register Table 2. Clock ...

Page 10

Table 38. Real-Time Clock Alarm Hours Register . . . . . . . . . . . . . . . . . . . . . . . . . . 102 Table 39. Real-Time Clock Alarm Day-of-the-Week ...

Page 11

Table 79 Clock Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 12

Table 120. Processor Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214 ...

Page 13

... Architectural Overview The eZ80F92 device is a high-speed single-cycle instruction-fetch microcontroller with a maximum clock speed of 20 MHz the first member of ZiLOG’s new eZ80Acclaim! product family, which offers on-chip Flash program memory. The eZ80F92 device can operate in Z80-compatible addressing mode (64 KB) or full 24-bit addressing mode (16 MB) ...

Page 14

General-Purpose I/O • • and ZDI debug interfaces • 100-pin LQFP package • 3.0–3.6 V supply voltage with 5 V tolerant inputs • Operating Temperature Range: Standard: 0ºC to +70ºC – – Extended: –40ºC to +105ºC ...

Page 15

I C SCL Serial Interface SDA SCK SPI Serial SS Parallel Interface MISO MOSI CTS0/1 DCD0/1 DSR0/1 UART Universal DTR0/1 Asynchronous Receiver/ RI0/1 Transmitter (2) RTS0/1 RXD0/1 TXD0/1 IrDA 8-bit General Encoder/ Decoder PS015308-0404 RTC_VDD Real-Time RTC_XIN Clock and ...

Page 16

Pin Description Figure 2 illustrates the pin layout of the eZ80F92 device in the 100-pin LQFP package. 100-Pin LQFP Pin Identification of the eZ80F92 Device describes the pins and their func- tions. ADDR0 1 ADDR1 2 ADDR2 3 ADDR3 4 ...

Page 17

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device Pin # Symbol Function 1 ADDR0 Address Bus 2 ADDR1 Address Bus 3 ADDR2 Address Bus 4 ADDR3 Address Bus 5 ADDR4 Address Bus 6 ADDR5 Address Bus PS015308-0404 Signal ...

Page 18

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 7 V Power Supply Ground SS 9 ADDR6 Address Bus 10 ADDR7 Address Bus 11 ADDR8 Address Bus 12 ADDR9 Address Bus ...

Page 19

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 14 ADDR11 Address Bus 15 ADDR12 Address Bus 16 ADDR13 Address Bus 17 ADDR14 Address Bus 18 V Power Supply Ground SS ...

Page 20

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 21 ADDR16 Address Bus 22 ADDR17 Address Bus 23 ADDR18 Address Bus 24 ADDR19 Address Bus 25 ADDR20 Address Bus 26 ADDR21 Address Bus PS015308-0404 ...

Page 21

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 27 ADDR22 Address Bus 28 ADDR23 Address Bus 29 CS0 Chip Select 0 30 CS1 Chip Select 1 31 CS2 Chip Select 2 32 CS3 ...

Page 22

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 37 DATA2 Data Bus 38 DATA3 Data Bus 39 DATA4 Data Bus 40 DATA5 Data Bus 41 DATA6 Data Bus 42 DATA7 Data Bus 43 ...

Page 23

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 47 RD Read 48 WR Write 49 INSTRD Instruction Read Indicator 50 WAIT WAIT Request Input, Active Low 51 RESET System Reset Schmitt Trigger Input, ...

Page 24

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 58 RTC_X Real-Time IN Clock Crystal Input 59 RTC_X Real-Time OUT Clock Crystal Output 60 RTC_V Real-Time DD Clock Power Supply 61 V Ground SS ...

Page 25

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 68 PD0 GPIO Port D TxD0 UART Transmit Data IR_TxD IrDA Transmit Data 69 PD1 GPIO Port D RxD0 Receive Data IR_RxD IrDA Receive Data ...

Page 26

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 71 PD3 GPIO Port D CTS0 Clear To Send Input, Active Low 72 PD4 GPIO Port D DTR0 Data Terminal Ready 73 PD5 GPIO Port ...

Page 27

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 75 PD7 GPIO Port D RI0 Ring Indicator Input, Active Low 76 PC0 GPIO Port C TxD1 Transmit Data Output 77 PC1 GPIO Port C ...

Page 28

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 78 PC2 GPIO Port C RTS1 Request To Send 79 PC3 GPIO Port C CTS1 Clear To Send Input, Active Low 80 PC4 GPIO Port ...

Page 29

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 82 PC6 GPIO Port C DCD1 Data Carrier Detect 83 PC7 GPIO Port C RI1 Ring Indicator Input, Active Low 84 V Ground SS 85 ...

Page 30

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 88 PB0 GPIO Port B T0_IN Timer PB1 GPIO Port B T1_IN Timer PB2 GPIO Port B SS Slave ...

Page 31

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 92 PB4 GPIO Port B T4_OUT Timer 4 Out 93 PB5 GPIO Port B T5_OUT Timer 5 Out 94 PB6 GPIO Port B MISO Master ...

Page 32

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued) Pin # Symbol Function 96 V Power Supply Ground SDA I C Serial Data Bidirectional 2 99 SCL I C Serial Clock 100 ...

Page 33

Table 2. Pin Characteristics of the eZ80F92 Device (Continued) Pin # Symbol Direction 16 ADDR13 I/O 17 ADDR14 I ADDR15 I/O 21 ADDR16 I/O 22 ADDR17 I/O 23 ADDR18 I/O 24 ADDR19 I/O ...

Page 34

Table 2. Pin Characteristics of the eZ80F92 Device (Continued) Pin # Symbol Direction IORQ I/O 46 MREQ I INSTRD O 50 WAIT I 51 RESET I 52 NMI I ...

Page 35

Table 2. Pin Characteristics of the eZ80F92 Device (Continued) Pin # Symbol Direction 71 PD3 I/O 72 PD4 I/O 73 PD5 I/O 74 PD6 I/O 75 PD7 I/O 76 PC0 I/O 77 PC1 I/O 78 PC2 I/O 79 PC3 I/O ...

Page 36

Table 2. Pin Characteristics of the eZ80F92 Device (Continued) Pin # Symbol Direction 99 SCL I/O 100 PHI O PS015308-0404 Reset Active Tristate Direction Low/High Output I N/A Yes O N/A Yes ...

Page 37

Register Map All on-chip peripheral registers are accessed in the I/O address space. All I/O operations employ 16-bit addresses. The upper byte of the 24-bit address bus is undefined during all I/O operations (ADDR[23:16] = range 0080h–00FFh not generated if ...

Page 38

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Programmable Reload Counter/Timers (continued) 0087 TMR2_DR_L Timer 2 Data Register—Low Byte TMR2_RR_L Timer 2 Reload Register—Low Byte 0088 TMR2_DR_H Timer 2 Data Register—High Byte TMR2_RR_H Timer 2 Reload Register—High Byte 0089 ...

Page 39

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Watch-Dog Timer 0093 WDT_CTL Watch-Dog Timer Control Register 0094 WDT_RR Watch-Dog Timer Reset Register General-Purpose Input/Output Ports 009A PB_DR Port B Data Register 009B PB_DDR Port B Data Direction Register 009C ...

Page 40

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Chip Select/Wait State Generator (continued) 00AE CS2_LBR Chip Select 2 Lower Bound Register 00AF CS2_UBR Chip Select 2 Upper Bound Register 00B0 CS2_CTL Chip Select 2 Control Register 00B1 CS3_LBR Chip ...

Page 41

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Universal Asynchronous Receiver/Transmitter 0 (UART0) Block 00C0 UART0_RBR UART 0 Receive Buffer Register UART0_THR UART 0 Transmit Holding Register UART0_BRG_L UART 0 Baud Rate Generator Register— Low Byte 00C1 UART0_IER UART ...

Page 42

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Universal Asynchronous Receiver/Transmitter 1 (UART1) Block 00D0 UART1_RBR UART 1 Receive Buffer Register UART1_THR UART 1 Transmit Holding Register UART1_BRG_L UART 1 Baud Rate Generator Register— Low Byte 00D1 UART1_IER UART ...

Page 43

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Real-Time Clock (continued) 00E4 RTC_DOM RTC Day-of-the-Month Register 00E5 RTC_MON RTC Month Register 00E6 RTC_YR RTC Year Register 00E7 RTC_CEN RTC Century Register 00E8 RTC_ASEC RTC Alarm Seconds Register 00E9 RTC_AMIN ...

Page 44

Table 3. Register Map (Continued) Address (hex) Mnemonic Name Flash Memory Control Registers (continued) 00FB FLASH_IRQ Flash Interrupt Control Register 00FC FLASH_PAGE Flash Page Select Register 00FD FLASH_ROW Flash Row Select Register 00FE FLASH_COL Flash Column Select Register 00FF FLASH_PGCTL ...

Page 45

... Nonmaskable Interrupt (NMI), plus support for 128 maskable vectored interrupts For more information on the eZ80 CPU User Manual (UM0077). For eZ80Acclaim! refer to the ZiLOG TCP/IP Software Suite Programmer’s Guide (RM0008), available upon registering your eZ80F92 or eZ80F93 product on PS015308-0404 ® ...

Page 46

Reset Reset Operation The Reset controller within the eZ80F92 device provides a consistent reset function for all types of resets that can affect the system. A system reset, referred to in this document as RESET, returns the eZ80F92 device to ...

Page 47

V POR V VBO V = 0.0V CC System Clock Oscillator Startup Internal RESET Signal Figure 3.Power-On Reset Operation Voltage Brown-Out Reset If, after program execution begins, the supply voltage (V Brown-Out threshold (V detects the low supply voltage and ...

Page 48

POR V VBO Program Execution System Clock Internal RESET Signal Figure 4.Voltage Brown-Out Reset Operation PS015308-0404 Voltage Brown-out RESET mode T timer delay ANA ...

Page 49

Low-Power Modes Overview The eZ80F92 device provides a range of power-saving features. The highest level of power reduction is provided by SLEEP mode. The next level of power reduction is pro- vided by the HALT instruction. The lowest level of ...

Page 50

Primary crystal oscillator is enabled and continues to operate • The system clock is enabled and continues to operate • The CPU is idle • The Program Counter (PC) stops incrementing The CPU can be brought out of HALT ...

Page 51

Table 4. Clock Peripheral Power-Down Register 1 (CLK_PPD1 = 00DBh) Bit Reset CPU Access Note: R/W = Read/Write Read Only. Bit Position 7 GPIO_D_OFF 6 GPIO_C_OFF 5 GPIO_B_OFF 4 3 SPI_OFF 2 I2C_OFF 1 UART1_OFF 0 UART0_OFF PS015308-0404 ...

Page 52

Table 5. Clock Peripheral Power-Down Register 2 (CLK_PPD2 = 00DCh) Bit Reset CPU Access Note: R/W = Read/Write Read Only. Bit Position 7 PHI_OFF 6 5 PRT5_OFF 4 PRT4_OFF 3 PRT3_OFF 2 PRT2_OFF 1 PRT1_OFF 0 PRT0_OFF PS015308-0404 ...

Page 53

General-Purpose Input/Output GPIO Overview The eZ80F92 device features 24 General-Purpose Input/Output (GPIO) pins. The GPIO pins are assembled as three 8-bit ports— Port B, Port C, and Port D. All port signals can be configured for use as either inputs ...

Page 54

Table 6. GPIO Mode Selection (Continued) GPIO Px_ALT2 Px_ALT1 Px_DDR Mode Bits7:0 Bits7 ...

Page 55

This bit enables a dual edge-triggered interrupt mode. Both a rising and a GPIO Mode 6. falling edge on the pin cause an interrupt request to be sent to the CPU. Writing the Port x Data register ...

Page 56

Data Bus D System Clock GPIO Register Data (Output) Figure 5.GPIO Port Pin Block Diagram GPIO Interrupts Each port pin can be used as an interrupt source. Interrupts can be either level- or edge- triggered. Level-Triggered Interrupts When the port ...

Page 57

Port x Data register causes a reset of the edge-detected interrupt. The programmer must set the bit in the Port x Data register to 1 before entering either single or dual edge-triggered interrupt ...

Page 58

Port x Data Direction Registers In conjunction with the other GPIO Control Registers, the Port x Data Direction registers, detailed in Port x Data Direction Registers (PB_DDR = 009Bh, PC_DDR = 009Fh, PD_DDR = 00A3h), control the operating modes of ...

Page 59

Interrupt Controller The interrupt controller on the eZ80F92 device routes the interrupt request signals from the internal peripherals and external devices (via the GPIO pins) to the CPU. Maskable Interrupts On the eZ80F92 device, all maskable interrupts use the CPU’s ...

Page 60

I[7:0], 00h 1Fh tine would be stored at {MBASE[7:0], I[7:0], significant byte is stored at the lower address. When any one or more of the interrupt requests (IRQs) become active, an interrupt request is generated by the interrupt ...

Page 61

Table 12. Vectored Interrupt Operation (Continued) Memory ADL MADL Mode Bit Bit Operation Z80 Mode 0 1 Read the LSB of the interrupt vector placed on the internal vectored interrupt bus, IVECT[7:0], bus by the interrupting peripheral. • IEF1 • ...

Page 62

Chip Selects and Wait States The eZ80F92 device generates four Chip Selects for external devices. Each Chip Select may be programmed to access either memory space or I/O space. The Memory Chip Selects can be individually programmed ...

Page 63

Memory Chip Select Priority A lower-numbered Chip Select is granted priority over a higher-numbered Chip Select. For example, if the address space of Chip Select 0 overlaps the Chip Select 1 address space, Chip Select 0 is active. Reset States ...

Page 64

Table 13. Register Values for Memory Chip Select Example in Figure 6 Chip CSx_CTL[3] CSx_CTL[4] Select CSx_EN CSx_IO CS0 1 0 CS1 1 0 CS2 1 0 CS3 1 0 I/O Chip Select Operation I/O Chip Selects can only be ...

Page 65

If all of the foregoing conditions are met to generate an I/O Chip Select, then the following actions occur: • The appropriate Chip Select—CS0, CS1, CS2, or CS3—is asserted (driven Low) • IORQ is asserted (driven Low) • Depending upon ...

Page 66

An example of WAIT state operation is illustrated in Figure 8. In this example, the Chip Select is configured to provide a single WAIT state. The external peripheral being accessed drives the WAIT pin Low to request assertion of an ...

Page 67

Bus Mode Controller The bus mode controller allows the address and data bus timing and signal formats of the eZ80F92 device to be configured to connect seamlessly with external eZ80 or Motorola-compatible devices. Bus modes for each of the chip ...

Page 68

Z80 Table 15. Bus Mode Write States STATE T1 The Write cycle begins in State T1. The CPU drives the address onto the address bus, the associated Chip Select signal is asserted. STATE T2 During State T2, the WR signal ...

Page 69

System Clock ADDR[23:0] DATA[7:0] CSx RD WAIT WR MREQ or IORQ Figure 10.Example: Z80 Bus Mode Write Timing Intel Bus Mode Chip selects configured for Intel bus mode modify the CPU bus signals to duplicate a four- state memory transfer ...

Page 70

Bus Mode Signals (Pins) INSTRD RD WR WAIT MREQ IORQ ADDR[23:0] DATA[7:0] Figure 11.Intel Bus Mode Signal and Pin Mapping Intel Bus Mode (Separate Address and Data Buses) During Read operations with separate address and data buses, the Intel ...

Page 71

Table 16. Intel Bus Mode Read States (Separate Address and Data Buses) STATE T3 During State T3, no bus signals are altered. If the external READY (WAIT) pin is driven Low at least one CPU system clock cycle prior to ...

Page 72

System Clock ADDR[23:0] DATA[7:0] CSx ALE RD READY WR MREQ or IORQ Figure 12.Example: Intel Bus Mode Read Timing—Separate Address and Data Buses PS015308-0404 WAIT ...

Page 73

System Clock ADDR[23:0] DATA[7:0] CSx ALE WR READY RD MREQ or IORQ Figure 13.Example: Intel Bus Mode Write Timing—Separate Address and Data Buses PS015308-0404 WAIT ...

Page 74

Intel Bus Mode (Multiplexed Address and Data Bus) During Read operations with multiplexed address and data, the Intel 4 states (T1, T2, T3, and T4) as described in Intel Bus Mode Read States (Multiplexed Address and Data Bus). Table 18. ...

Page 75

Signal timing for Intel bus mode with multiplexed address and data is illustrated for a Read operation in Figure 14 and for a Write operation in Figure 15. In the figures, each TM Intel bus mode state is 2 CPU ...

Page 76

System Clock ADDR[23:0] DATA[7:0] CSx ALE WR READY RD MREQ or IORQ Figure 15.Example: Intel Bus PS015308-0404 Bus Mode Write Timing—Multiplexed Address and Data ...

Page 77

Motorola Bus Mode Chip selects configured for Motorola bus mode modify the CPU bus signals to duplicate an eight-state memory transfer similar to that found on Motorola-style microcontrollers. The bus signals (and eZ80F92 I/O pins) are mapped as illustrated in ...

Page 78

Table 20. Motorola Bus Mode Read States (Continued) STATE S4 During state S4, the CPU waits for a cycle termination signal DTACK (WAIT), a peripheral signal. If the termination signal is not asserted at least one full CPU clock period ...

Page 79

Signal timing for Motorola bus mode is illustrated for a Read operation in Figure 17 and for a Write operation in Figure 18. In these two figures, each Motorola bus mode state is 2 CPU system clock cycles in duration. ...

Page 80

S0 System Clock ADDR[23:0] DATA[7:0] CSx AS DS R/W DTACK MREQ or IORQ Figure 18.Example: Motorola Bus Mode Write Timing Switching Between Bus Modes Each time the bus mode controller must switch from one bus mode to another, there is ...

Page 81

Chip Select Registers Chip Select x Lower Bound Register For Memory Chip Selects, the Chip Select x Lower Bound register, detailed in Chip Select x Lower Bound Register (CS0_LBR = 00A8h, CS1_LBR = 00ABh, CS2_LBR = 00AEh, CS3_LBR = 00B1h), ...

Page 82

Chip Select x Upper Bound Register For Memory Chip Selects, the Chip Select x Upper Bound registers, detailed in Chip Select x Upper Bound Register (CS0_UBR = 00A9h, CS1_UBR = 00ACh, CS2_UBR = 00AFh, CS3_UBR = 00B2h), defines the upper ...

Page 83

Table 24. Chip Select x Control Register (CS0_CTL = 00AAh, CS1_CTL = 00ADh, CS2_CTL = 00B0h, CS3_CTL = 00B3h) Bit CS0_CTL Reset CS1_CTL Reset CS2_CTL Reset CS3_CTL Reset CPU Access Note: R/W = Read/Write Read Only. Bit Position ...

Page 84

Table 25. Chip Select x Bus Mode Control Register (CS0_BMC = 00F0h, CS1_BMC = 00F1h, CS2_BMC = 00F2h, CS3_BMC = 00F3h) Bit CS0_BMC Reset CS1_BMC Reset CS2_BMC Reset CS3_BMC Reset CPU Access Note: R/W = Read/Write Read Only. ...

Page 85

Bit Position [3:0] BUS_CYCLE Notes: 1. Setting BUS_CYCLE Intel bus mode causes the ALE pin to not function properly. 2. Use of the external WAIT input pin in Z80 mode requires that BUS_CYCLE is set to a ...

Page 86

Watch-Dog Timer Watch-Dog Timer Overview The Watch-Dog Timer (WDT) helps protect against corrupt or unreliable software, power faults, and other system-level problems which may place the CPU into unsuitable operat- ing states. The eZ80F92 WDT features: • Four programmable time-out ...

Page 87

Watch-Dog Timer Operation Enabling and Disabling the WDT The Watch-Dog Timer is disabled upon a RESET. To enable the WDT, the application pro- gram must set the WDT_EN bit (bit 7) of the WDT_CTL register. When enabled, the WDT cannot ...

Page 88

If the NMI_OUT bit in the WDT_CTL register is set to 1, then upon time-out, the WDT asserts an NMI for CPU processing. The NMI_FLAG bit can be polled by the CPU to determine the source of the NMI event. ...

Page 89

Bit Position 2 [1:0] WDT_PERIOD Note: *RST_FLAG is only cleared by a non-WDT RESET. Watch-Dog Timer Reset Register The Watch-Dog Timer Reset register, detailed in Watch-Dog Timer Reset Register bit Write Only register. The Watch-Dog Timer is ...

Page 90

Programmable Reload Timers Programmable Reload Timers Overview The eZ80F92 device features six Programmable Reload Timers (PRT). Each PRT contains a 16-bit downcounter and a 16-bit reload register. In addition, each PRT features a clock prescaler with four selectable taps for ...

Page 91

Programmable Reload Timer Operation Setting Timer Duration There are three factors to consider when determining Programmable Reload Timer dura- tion—clock frequency, clock divider ratio, and initial count value. Minimum duration of the timer is achieved by loading , because the ...

Page 92

CLK CLKEN IOWRN t [7:0] CNTH t [7:0] CNTL IRQ Figure 21.PRT SINGLE PASS Mode Operation Example Table 29. PRT SINGLE PASS Mode Operation Example Parameter PRT Enabled Reload and Restart Enabled PRT Clock Divider = 4 SINGLE PASS Mode ...

Page 93

CLK PRT Clock (Clock ÷ 4) IOWRN PRT Count X Value Interrupt Request Table 30. PRT CONTINUOUS Mode Operation Example Table 31. PRT CONTINUOUS Mode Operation Example Parameter PRT Enabled Reload and Restart Enabled PRT Clock Divider = 4 CONTINUOUS ...

Page 94

Then, when the end-of-count value, rupt service request signal is passed to the CPU. PRT_IRQ is cleared to 0 and the interrupt service request signal is inactivated whenever the CPU reads from the timer control regis- ters, TMRx_CTL. Timer Input ...

Page 95

CLK PRT Clock (Clock ÷ 4) IOWRN PRT Count X Value Timer Output Figure 22.PRT Timer Output Operation Example Table 32. PRT Timer Out Operation Example Parameter PRT Enabled Reload and Restart Enabled PRT Clock Divider = 4 CONTINUOUS Mode ...

Page 96

CONTINUOUS and SINGLE PASS modes, and enabling the auto-reload feature. PS015308-0404 eZ80F92/eZ80F93 Product Specification 84 Programmable Reload ...

Page 97

Table 33. Timer Control Register (TMR0_CTL = 0080h, TMR1_CTL = 0083h, TMR2_CTL = 0086h, TMR3_CTL = 0089h, TMR4_CTL = 008Ch, or TMR5_CTL = 008Fh) Bit Reset CPU Access Note Read only; R/W = Read/Write. Bit Position Value 7 ...

Page 98

Timer Data Register—Low Byte This Read Only register returns the Low byte of the current count value of the selected timer. The Timer Data Register—Low Byte, detailed in Timer Data Register—Low Byte (TMR0_DR_L = 0081h, TMR1_DR_L = 0084h, TMR2_DR_L = ...

Page 99

Table 35. Timer Data Register—High Byte (TMR0_DR_H = 0082h, TMR1_DR_H = 0085h, TMR2_DR_H = 0088h, TMR3_DR_H = 008Bh, TMR4_DR_H = 008Eh, or TMR5_DR_H = 0091h) Bit Reset CPU Access Note Read only. Bit Position Value [7:0] 00h–FFh These ...

Page 100

Timer Reload Register—High Byte The Timer Reload Register—High Byte, detailed in Timer Reload Register—High Byte (TMR0_RR_H = 0082h, TMR1_RR_H = 0085h, TMR2_RR_H = 0088h, TMR3_RR_H = 008Bh, TMR4_RR_H = 008Eh, or TMR5_RR_H = 0091h), stores the most-significant byte (MSB) of ...

Page 101

Table 38. Timer Input Source Select Register (TMR_ISS = 0092h) Bit Reset CPU Access Note: R/W = Read/Write. Bit Position [7:6] TMR3_IN [5:4] TMR2_IN [3:2] TMR1_IN [1:0] TMR0_IN PS015308-0404 R/W R/W R/W R/W Value ...

Page 102

Real-Time Clock Real-Time Clock Overview The Real-Time Clock (RTC) keeps time by maintaining a count of seconds, minutes, hours, day-of-the-week, day-of-the-month, year, and century. The current time is kept in 24-hour format. The format for all count and alarm registers ...

Page 103

Real-Time Clock Alarm The clock can be programmed to generate an alarm condition when the current count matches the alarm set-point registers. Alarm registers are available for seconds, minutes, hours, and day-of-the-week. Each alarm can be independently enabled. To generate ...

Page 104

Write to RTC_CTRL to clear the RTC_UNLOCK bit; clearing the RTC_UNLOCK bit resets and enables the clock divider Real-Time Clock Registers The Real-Time Clock registers are accessed via the address and data bus using I/O instruc- tions. RTC_UNLOCK controls ...

Page 105

Real-Time Clock Minutes Register This register contains the current minutes count. See Real-Time Clock Minutes Register (RTC_MIN = 00E1h). Table 40. Real-Time Clock Minutes Register (RTC_MIN = 00E1h) Bit Reset CPU Access Note Unchanged by RESET; R/W* = ...

Page 106

Real-Time Clock Hours Register This register contains the current hours count. See Real-Time Clock Hours Register (RTC_HRS = 00E2h). Table 41. Real-Time Clock Hours Register (RTC_HRS = 00E2h) Bit Reset CPU Access Note Unchanged by RESET; R/W* = ...

Page 107

Real-Time Clock Day-of-the-Week Register This register contains the current day-of-the-week count. The RTC_DOW register begins counting at . See Real-Time Clock Day-of-the-Week Register (RTC_DOW = 00E3h). 01h Table 42. Real-Time Clock Day-of-the-Week Register (RTC_DOW = 00E3h) Bit Reset CPU Access ...

Page 108

Real-Time Clock Day-of-the-Month Register This register contains the current day-of-the-month count. The RTC_DOM register begins counting at . See Real-Time Clock Day-of-the-Month Register (RTC_DOM = 00E4h). 01h Table 43. Real-Time Clock Day-of-the-Month Register (RTC_DOM = 00E4h) Bit Reset CPU Access ...

Page 109

Real-Time Clock Month Register This register contains the current month count. See Real-Time Clock Month Register (RTC_MON = 00E5h). Table 44. Real-Time Clock Month Register (RTC_MON = 00E5h) Bit Reset CPU Access Note Unchanged by RESET; R/W* = ...

Page 110

Real-Time Clock Year Register This register contains the current year count. See Real-Time Clock Year Register (RTC_YR = 00E6h). Table 45. Real-Time Clock Year Register (RTC_YR = 00E6h) Bit Reset CPU Access Note Unchanged by RESET; R/W* = ...

Page 111

Real-Time Clock Century Register This register contains the current century count. See Real-Time Clock Century Register (RTC_CEN = 00E7h). Table 46. Real-Time Clock Century Register (RTC_CEN = 00E7h) Bit Reset CPU Access Note Unchanged by RESET; R/W* = ...

Page 112

Real-Time Clock Alarm Seconds Register This register contains the alarm seconds value. See Real-Time Clock Alarm Seconds Reg- ister (RTC_ASEC = 00E8h). Table 47. Real-Time Clock Alarm Seconds Register (RTC_ASEC = 00E8h) Bit Reset CPU Access Note Unchanged ...

Page 113

Real-Time Clock Alarm Minutes Register This register contains the alarm minutes value. See Real-Time Clock Alarm Minutes Reg- ister (RTC_AMIN = 00E9h). Table 48. Real-Time Clock Alarm Minutes Register (RTC_AMIN = 00E9h) Bit Reset CPU Access Note Unchanged ...

Page 114

Real-Time Clock Alarm Hours Register This register contains the alarm hours value. See Real-Time Clock Alarm Hours Register (RTC_AHRS = 00EAh). Table 49. Real-Time Clock Alarm Hours Register (RTC_AHRS = 00EAh) Bit Reset CPU Access Note Unchanged by ...

Page 115

Real-Time Clock Alarm Day-of-the-Week Register This register contains the alarm day-of-the-week value. See Real-Time Clock Alarm Day- of-the-Week Register (RTC_ADOW = 00EBh). Table 50. Real-Time Clock Alarm Day-of-the-Week Register (RTC_ADOW = 00EBh) Bit Reset CPU Access Note Unchanged ...

Page 116

Real-Time Clock Alarm Control Register This register contains alarm enable bits for the Real-Time Clock. The RTC_ACTRL regis- ter is cleared by a RESET. See Real-Time Clock Alarm Control Register (RTC_ACTRL = 00ECh). Table 51. Real-Time Clock Alarm Control Register ...

Page 117

CLK_SEL and FREQ_SEL select the RTC clock source. If the 32 KHz crystal option is selected the oscillator is enabled and the internal prescaler is set to divide by 32768. If the power-line frequency option is selected, the prescale value ...

Page 118

Universal Asynchronous Receiver/ Transmitter The UART module implements all of the logic required to support several asynchronous communications protocols. The module also implements two separate 16-byte-deep FIFOs for both transmission and reception. A block diagram of the UART is illustrated ...

Page 119

UART Functional Description The UART function implements: • The transmitter and associated control logic • The receiver and associated control logic • The modem interface and associated logic UART Functions The UART function implements: • The transmitter and associated control ...

Page 120

UART Receiver The receiver block controls the data reception from the RxD signal. The receiver ...

Page 121

UART Transmitter Interrupt The transmitter hold register empty interrupt is generated if there is no data available in the hold register. The transmission complete interrupt is generated after the data in the shift register is sent. Both interrupts can be ...

Page 122

UART Recommended Usage The following is the standard sequence of events that occur in the eZ80F92 device using the UART. A description of each follows. • Module reset • Control transfers to configure UART operation • Data transfers Module Reset ...

Page 123

If the interrupt is caused by a receive-data-ready condition, the application alternately reads the UARTx_LSR and UARTx_RBR registers and removes all of the received data bytes. It reads the UARTx_LSR ...

Page 124

Program the UARTx_BRG_L and UARTx_BRG_H registers • Clear UARTx_LCTL[ disable access of the BRG divisor registers BRG Control Registers UART Baud Rate Generator Register—Low and High Bytes The registers hold the Low and High bytes of ...

Page 125

Table 54. UART Baud Rate Generator Register—High Bytes (UART0_BRG_H = 00C1h, UART1_BRG_H = 00D1h) Bit Reset CPU Access Note Read only; R/W = Read/Write. Bit Position [7:0] UART_BRG_H UART Registers After a RESET, all UART registers are set ...

Page 126

Table 55. UART Transmit Holding Registers (UART0_THR = 00C0h, UART1_THR = 00D0h) Bit Reset CPU Access Note Write only. Bit Position [7: UART Receive Buffer Register The bits in this register reflect the data received. ...

Page 127

UART Interrupt Enable Register The UARTx_IER register is used to enable and disable the UART interrupts. The UARTx_IER registers share the same I/O addresses as the UARTx_BRG_H registers. See UART Interrupt Enable Registers (UART0_IER = 00C1h, UART1_IER = 00D1h). Table ...

Page 128

UART Interrupt Identification Register The Read Only UARTx_IIR register allows the user to check whether the FIFO is enabled and the status of interrupts. These registers share the same I/O addresses as the UARTx_FCTL registers. See Tables 58 and 59. ...

Page 129

Table 59. UART Interrupt Status Codes (Continued) INSTS Value Priority 001 Fifth 000 Lowest UART FIFO Control Register This register is used to monitor trigger levels, clear FIFO pointers, and enable or disable the FIFO. The UARTx_FCTL registers share the ...

Page 130

Bit Position 2 CLRTXF 1 CLRRXF 0 FIFOEN Note: *Receive FIFO is not enabled during UART Line Control Register This register is used to control the communication control parameters. See Tables 61 and 62. Table 61. UART Line Control Registers ...

Page 131

Bit Position FPE 4 EPS 3 PEN [2:0] CHAR Note: *Receive Parity is set to SPACE in MULTIDROP mode. PS015308-0404 Value Description 0 Do not send a BREAK signal. 1 Send Break UART sends continuous zeroes on ...

Page 132

Table 62. UART Character Parameter Definition CHAR[2:0] 000 001 010 011 100 101 110 111 Table 63. Parity Select Definition for Multidrop Communications MDM UARTx_MGTL[ Note: *In MULTIDROP mode, EPS resets to 0 after the first ...

Page 133

UART Modem Control Register This register is used to control and check the modem status, as detailed in UART Modem Control Registers (UART0_MCTL = 00C4h, UART1_MCTL = 00D4h). Table 64. UART Modem Control Registers (UART0_MCTL = 00C4h, UART1_MCTL = 00D4h) ...

Page 134

Bit Position 1 RTS 0 DTR UART Line Status Register This register is used to show the status of UART interrupts and registers. See UART Line Status Registers (UART0_LSR = 00C5h, UART1_LSR = 00 D5h). Table 65. UART Line Status ...

Page 135

Bit Position 5 THRE PS015308-0404 Value Description 0 Transmit holding register/FIFO is not empty. 1 Transmit holding register/FIFO is empty. This bit cannot be set to 1 during the BREAK condition. This ...

Page 136

Bit Position 0 DR UART Modem Status Register This register is used to show the status of the UART signals. See UART Modem Status Registers (UART0_MSR = 00C6h, UART1_MSR = 00 D6h). Table 66. UART Modem Status Registers (UART0_MSR = ...

Page 137

Bit Position 3 DDCD 2 TERI 1 DDSR 0 DCTS UART Scratch Pad Register The UARTx_SPR register can be used by the system as a general-purpose Read/Write reg- ister. See UART Scratch Pad Registers (UART0_SPR = 00C7h, UART1_SPR = 00D7h). ...

Page 138

Infrared Encoder/Decoder The eZ80F92 device contains a UART to infrared encoder/decoder (endec). The IrDA endec is integrated with the on-chip UART0 to allow easy communication between the CPU and IrDA Physical Layer Specification Version 1.4-compatible infrared transceivers, as illustrated in ...

Page 139

Refer to the Universal Asynchronous Receiver/Transmitter section on page 106 for more information on the UART and its Baud Rate Generator. Transmit The data to be transmitted via the IR transceiver is first sent to UART0. The UART trans- ...

Page 140

The UART baud rate clock is used by the IrDA endec to generate the demodulated signal (RxD) that drives the UART. Each UART bit period is sixteen baud-clocks wide. Each IR_RXD bit is encoded during a bit period such that ...

Page 141

Table 68. IrDA Physical Layer 1.4 Pulse Durations Specifications Baud Rate 57600 115200 Receiver Frequency Divider The IrDA receiver uses a 6-bit frequency divider. The value is derived from the system clock to measure IR_RxD pulses. The IrDA endec detects ...

Page 142

Setting the upper 4 bits of IR_CTL to receiver. In this mode, the IrDA receiver uses edge detection on the IR_RxD bit stream. Jitter Due to the inherent sampling of the received IR_RxD signal by the BIt Rate Clock, some ...

Page 143

Infrared Encoder/Decoder Register After a RESET, the Infrared Encoder/Decoder register is set to its default value. Any writes to unused register bits are ignored and reads return a value of 0. The IR_CTL regis- ter is described in Infrared Encoder/Decoder ...

Page 144

Serial Peripheral Interface The Serial Peripheral Interface (SPI synchronous interface allowing several SPI-type devices to be interconnected. The SPI is a full-duplex, synchronous, character-oriented communication channel that employs a four-wire interface. The SPI block consists of a transmitter, ...

Page 145

SPI Signals The four basic SPI signals are: • MISO (Master In, Slave Out) • MOSI (Master Out, Slave In) • SCK (SPI Serial Clock) • SS (Slave Select) These SPI signals are discussed in the following paragraphs. Each signal ...

Page 146

SCK pin becomes an input on a slave device. The SPI contains an internal divide-by-two clock divider. In MASTER mode, the SPI serial clock is one-half the frequency of the clock signal created by the ...

Page 147

SPI Functional Description When a master transmits to a slave device via the MOSI signal, the slave device responds by sending data to the master via the master's MISO signal. The resulting implication is a full-duplex transmission, with both data ...

Page 148

If the SPI interrupt is enabled by setting IRQ_EN (SPI_CTL[7]) High, an SPI interrupt is generated. Clearing the Mode Fault flag is performed by reading the SPI Status register. The other SPI control bits (SPI_EN and MASTER_EN) must be ...

Page 149

Assert the ENABLE pin of the slave device using a GPIO pin. 5. Load the SPI Transmit Shift Register, SPI_TSR. 6. When the SPI data transfer is complete, deassert the ENABLE pin of the slave device. Data Transfer Procedure ...

Page 150

PS015308-0404 eZ80F92/eZ80F93 Product Specification 138 Serial Peripheral Interface ...

Page 151

Table 74. SPI Baud Rate Generator Register—High Byte (SPI_BRG_H = 00B9h) Bit Reset CPU Access Note: R/W = Read/Write. Bit Position [7:0] SPI_BRG_H SPI Control Register This register is used to control and setup the serial peripheral interface. The SPI ...

Page 152

Bit Position 2 CPHA [1:0] SPI Status Register The SPI Status Read Only register returns the status of data transmitted using the serial peripheral interface. Reading the SPI_SR register clears Bits 7, 6, and logical 0. See ...

Page 153

SPI Transmit Shift Register The SPI Transmit Shift register (SPI_TSR) is used by the SPI master to transmit data onto the SPI serial bus to the slave device. A Write to the SPI_TSR register places data directly into the shift ...

Page 154

I2C Serial I/O Interface General Characteristics 2 The I C serial I/O bus is a two-wire communication interface that can operate in four modes: • MASTER TRANSMIT • MASTER RECEIVE • SLAVE TRANSMIT • SLAVE RECEIVE 2 ...

Page 155

Data Validity The data on the SDA line must be stable during the High period of the clock. The High or Low state of the data line can only change when the clock signal on the SCL line is Low ...

Page 156

Transferring Data Byte Format Every character transferred on the SDA line must be a single 8-bit byte. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge (ACK) Figure 33. ...

Page 157

STOP or a repeated START condition. Data Output by Transmitter Data Output by Receiver SCL Signal from Master START Condition 2 Figure 34.I C Acknowledge Clock Synchronization ...

Page 158

CLK1 Signal CLK2 Signal SCL Signal Figure 35.Clock Synchronization In I Arbitration A master may start a transfer only if the bus is free. Two or more masters may generate a START condition within the minimum hold time of the ...

Page 159

A STOP condition and a data bit • A repeated START condition and a STOP condition Clock Synchronization for Handshake The Clock synchronizing mechanism can function as a handshake, enabling receivers to cope with fast data transfers, on either ...

Page 160

Table 79 Master Transmit Status Codes 2 Code I C State 18h Addr+W transmitted, ACK received 20h Addr+W transmitted, ACK not received 38h Arbitration lost 68h Arbitration lost, +W received, ACK transmitted 78h Arbitration lost, General call ...

Page 161

Table 80 10-Bit Master Transmit Status Codes 2 Code I C State 38h Arbitration lost 68h Arbitration lost, SLA+W received, ACK transmitted B0h Arbitration lost, SLA+R received, ACK transmitted D0h Second Address byte + W transmitted, ACK ...

Page 162

Table 81 Master Transmit Status Codes For Data Bytes (Continued) 2 Code I C State Data byte 30h transmitted, ACK not received Arbitration lost 38h When all bytes are transmitted, the microcontroller should write ...

Page 163

Table 82 Master Receive Status Codes 2 Code I C State 48h Addr + R transmitted, ACK not received 38h Arbitration lost 68h Arbitration lost, SLA+W received, ACK transmitted 78h Arbitration lost, General call addr received, ACK ...

Page 164

Table 83 Master Receive Status Codes For Data Bytes 2 Code I C State Data byte received, 50h ACK transmitted Data byte received, 58h NACK transmitted Arbitration lost in 38h NACK bit When all bytes are received, ...

Page 165

IFLG is set and the the idle state. The AAK bit must be set to 1 before reentering SLAVE mode acknowledge is received after transmitting a byte, the IFLG is set and the register contains ...

Page 166

I C Registers Addressing The processor interface provides access to six 8-bit registers: four Read/Write registers, one Read Only register and two Write Only registers, as indicated in I tions. 2 Table 84 Register Descriptions Register I2C_SAR ...

Page 167

The full 10-bit address is supplied by {I2C_SAR[2:1], I2C_XSAR[7:0]}. See I 2 Table 85 Slave Address Registers (I2C_SAR = 00C8h) Bit Reset CPU Access Note: R/W = Read/Write. Bit Position [7:1] SLA 0 GCE ...

Page 168

Table 86 Extended Slave Address Registers (I2C_XSAR = 00C9h) Bit Reset CPU Access Note: R/W = Read/Write. Bit Position [7:0] SLAX Data Register This register contains the data byte/slave address to be transmitted or ...

Page 169

I C responds to calls to its slave address and to the general call address if the GCE bit (I2C_SAR[0]) is set to 1. When the Master Mode Start bit (STA) is set to 1, ...

Page 170

Table 88 Control Registers (I2C_CTL = 00CBh) Bit Reset CPU Access Note: R/W = Read/Write Read Only. Bit Position 7 IEN 6 ENAB 5 STA 4 STP 3 IFLG 2 AAK [1:0] PS015308-0404 7 6 ...

Page 171

I C Status Register The I2C_SR register is a Read Only register that contains a 5-bit status code in the five most-significant bits: the three least-significant bits are always 0. The Read Only I2C_SR registers share the same I/O ...

Page 172

Table 90 Status Codes (Continued) Code Status Address and Read bit transmitted, ACK received 40h Address and Read bit transmitted, ACK not received 48h Data byte received in MASTER mode, ACK transmitted 50h Data byte received in ...

Page 173

I C Clock Control Register The I2C_CCR register is a Write Only register. The seven LSBs control the frequency at 2 which the I C bus is sampled and the frequency of the MASTER mode. The ...

Page 174

Bus Clock Speed 2 The I C bus is defined for bus clock speeds up to 100 KBPS (400 KBPS in FAST mode). To ensure correct detection of START and STOP conditions on the bus, the I 2 ple the ...

Page 175

... C source-level debugging using ZiLOG Developer Studio (ZDS II) The above features are built into the silicon. Control is provided via a two-wire interface that is connected to the ZPAK II Debug Interface Tool. Figure 36 illustrates a typical setup using a a target board, ZPAK II, and the host PC running ZiLOG Developer Studio. Refer to the ZiLOG website ...

Page 176

... ZDA pin is shared with the TDI pin. The ZCL and ZDA pin functions are PS015308-0404 ZDI Clock Frequency 1 Mhz 2 Mhz 4 Mhz 8 Mhz 330 KΩ 330 KΩ 6-Pin Target Connector eZ80F92/eZ80F93 Product Specification TV DD (Target ZiLOG Debug Interface 164 ...

Page 177

... ZCL as illustrated in Figure 39. When an operation is completed, the master stops during the ninth cycle and holds the ZCL signal High. ZCL ZDA Start Signal Figure 38.ZDI Write Timing PS015308-0404 ZDI Data In ZDI Data In (Write) (Write eZ80F92/eZ80F93 Product Specification 165 ZiLOG Debug Interface ...

Page 178

... Write operation depending on the state of the R/W bit (0 = Write Read new START command is issued at completion of the Read or Write operation, the operation PS015308-0404 ZDI Data Out (Read) returns the eZ80 Product ID Low Byte while a Write to this same eZ80F92/eZ80F93 Product Specification ZDI Data Out (Read) ZiLOG Debug Interface 166 ...

Page 179

... Figure 41.ZDI Single-Byte Data Write Timing PS015308-0404 ZDI Address Byte msb ZDI Data Byte msb of DATA eZ80F92/eZ80F93 Product Specification Single-Bit Byte Separator or new ZDI START Signal R/W 0/1 lsb 0 = WRITE 1 = READ lsb of DATA End of Data or New ZDI START Signal ZiLOG Debug Interface 167 ...

Page 180

... The most-significant bit (msb) is shifted out first. Figure 43 illustrates the timing for ZDI single-byte Read operations. PS015308-0404 ZDI Data Bytes msb lsb of DATA of DATA Byte 1 Byte 1 Byte Separator eZ80F92/eZ80F93 Product Specification 0 msb of DATA Byte 2 Single-Bit ZiLOG Debug Interface 168 ...

Page 181

... BREAK point. PS015308-0404 ZDI Data Byte msb of DATA ZDI Data Bytes msb lsb of DATA of DATA Byte 1 Byte 1 Byte Separator eZ80F92/eZ80F93 Product Specification lsb of DATA End of Data or New ZDI START Signal ), the address 20h 0 msb of DATA Byte 2 Single-Bit ZiLOG Debug Interface 169 ...

Page 182

... To prevent data errors, ZDI should avoid data transmission while another device is controlling the bus. Finally, exiting ZDI DEBUG mode while an external peripheral controls the address and data buses, as indicated by BUSACK assertion, may produce unpredictable results. PS015308-0404 eZ80F92/eZ80F93 Product Specification 170 ZiLOG Debug Interface ...

Page 183

... Instruction Store 1 Instruction Store 0 Write Memory register eZ80F92/eZ80F93 Product Specification 171 Reset Value XXh XXh XXh XXh XXh XXh XXh XXh XXh XXh XXh XXh 00h 00h XXh XXh XXh 00h 00h XXh XXh XXh XXh XXh XXh ZiLOG Debug Interface ...

Page 184

... Read Memory Address Low Byte register Read Memory Address High Byte register Read Memory Address Upper Byte register Bus Status register Read Memory Data Value eZ80F92/eZ80F93 Product Specification 172 Reset Value 07h 00h XXh 00h XXh XXh XXh 00h XXh ZiLOG Debug Interface ...

Page 185

... ZDI_ADDR3_L = 0Ch, ZDI_ADDR3_H = 0Dh, and ZDI_ADDR3_U = 0Eh in the ZDI Register Write Only Address Space. PS015308-0404 eZ80F92/eZ80F93 Product Specification 173 ZiLOG Debug Interface ...

Page 186

... BREAK. See ZDI BREAK Control Register. PS015308-0404 Value Description 00h– The four sets of ZDI address match registers are used for FFh setting the addresses for generating BREAK points. The 24-bit addresses are supplied by {ZDI_ADDRx_U, ZDI_ADDRx_H, ZDI_ADDRx_L, where eZ80F92/eZ80F93 Product Specification ZiLOG Debug Interface 174 ...

Page 187

... The ZDI BREAK, upon matching BREAK address 1, is disabled. 1 The ZDI BREAK, upon matching BREAK address 1, is enabled. 0 The ZDI BREAK, upon matching BREAK address 0, is disabled. 1 The ZDI BREAK, upon matching BREAK address 0, is enabled eZ80F92/eZ80F93 Product Specification ZiLOG Debug Interface 175 ...

Page 188

... ADDR[23:8], match the 2 bytes value {ZDI_ADDR0_U, ZDI_ADDR0_H result, a BREAK can occur anywhere within a 256-byte page. 0 ZDI SINGLE STEP mode is disabled. 1 ZDI SINGLE STEP mode is enabled. ZDI asserts a BREAK following execution of each instruction eZ80F92/eZ80F93 Product Specification 176 ZiLOG Debug Interface ...

Page 189

... ZDI Register Write Address Spaces) Bit Reset CPU Access Note Write Only. Bit Position 7 ZDI_RESET [6:0] PS015308-0404 Value Description 0 No action. 1 Initiate a RESET of the CPU. This bit is automatically cleared at the end of the RESET event. 0000000 Reserved eZ80F92/eZ80F93 Product Specification ZiLOG Debug Interface 177 ...

Page 190

... Write operation defined by the ZDI_RW_CTL register. The 24-bit data value is stored as {ZDI_WR_U, ZDI_WR_H, ZDI_WR_L}. If less than 24 bits of data are required to complete the required operation, the data is taken from the least-significant byte(s eZ80F92/eZ80F93 Product Specification 16h ZiLOG Debug Interface 178 ...

Page 191

... ZDI_WR_H E ZDI_WR_L Write HL HLU ZDI_WR_U H ZDI_WR_H L ZDI_WR_L Write IX IXU ZDI_WR_U IXH ZDI_WR_H IXL ZDI_WR_L Write IY IYU ZDI_WR_U IYH ZDI_WR_H IYL ZDI_WR_L Write SP In ADL mode SPL. In Z80 mode SPS. Write PC PC[23:16] ZDI_WR_U PC[15:8] ZDI_WR_H PC[7:0] ZDI_WR_L Reserved ZiLOG Debug Interface 179 ...

Page 192

... The ZDI programmer must execute the exchange instruction (EXX) to gain access to the alternate eZ80 PS015308-0404 Hex Value AF’ BC’ DE’ HL’ 8B ® CPU register set eZ80F92/eZ80F93 Product Specification Command Reserved Reserved Write memory from current PC value, increment PC ZiLOG Debug Interface 180 ...

Page 193

... Deassert the bus acknowledge pin (BUSACK) to return control of the address and data buses back to ZDI. 1 Assert the bus acknowledge pin (BUSACK) to pass control of the address and data buses to an external peripheral. 000000 Reserved eZ80F92/eZ80F93 Product Specification 181 ZiLOG Debug Interface ...

Page 194

... These registers contain the Op Codes and operands for FFh immediate execution by the CPU following a Write to ZDI_IS0. The ZDI_IS0 register contains the first Op Code of the instruction. The remaining ZDI_ISx registers contain any additional Op Codes or operand dates required for execution of the required instruction eZ80F92/eZ80F93 Product Specification ZiLOG Debug Interface 182 ...

Page 195

... Write to this address is written to the address indicated by the current program counter. The program counter is incremented following each 8 bits of data. In Z80 MEMORY mode, ({MBASE, PC[15:0]}) transferred data. In ADL MEMORY mode, (PC[23:0]) 8-bits of transferred data eZ80F92/eZ80F93 Product Specification bits of ZiLOG Debug Interface 183 ...

Page 196

... Note Read Only. Bit Position [7:0] ZDI_ID_H PS015308-0404 Value Description 07h {ZDI_ID_H, ZDI_ID_L} = {00h, 07h} indicates the eZ80F92 product Value Description 00h {ZDI_ID_H, ZDI_ID_L} = {00h, 07h} indicates the eZ80F92 product eZ80F92/eZ80F93 Product Specification ™ product being addressed. See ZiLOG Debug Interface 184 ...

Page 197

... Identifies the current revision of the eZ80F92 product. FFh Value Description 0 The CPU is not functioning in ZDI mode. 1 The CPU is currently functioning in ZDI mode. 0 Reserved. 0 The CPU is not currently in HALT or SLEEP mode. 1 The CPU is currently in HALT or SLEEP mode eZ80F92/eZ80F93 Product Specification 185 ZiLOG Debug Interface ...

Page 198

... The CPU’s Interrupt Enable Flag 1 is set to 1. Maskable interrupts are enabled. 00 Reserved Value Description 00h– Values read from the memory location as requested by FFh the ZDI Read Control register during a ZDI Read operation. The 24-bit value is supplied by {ZDI_RD_U, ZDI_RD_H, ZDI_RD_L eZ80F92/eZ80F93 Product Specification 186 ZiLOG Debug Interface ...

Page 199

... Address and data buses are not relinquished to an external peripheral. bus acknowledge is deasserted (BUSACK pin is High). 1 Address and data buses are relinquished to an external peripheral. bus acknowledge is asserted (BUSACK pin is Low). 000000 Reserved eZ80F92/eZ80F93 Product Specification 187 ZiLOG Debug Interface ...

Page 200

... PS015308-0404 eZ80F92/eZ80F93 Product Specification 188 ZiLOG Debug Interface ...