DSP56301PW80B1 Freescale Semiconductor, DSP56301PW80B1 Datasheet - Page 58

DSP56301PW80B1

Manufacturer Part Number

DSP56301PW80B1

Description

Manufacturer

Freescale Semiconductor

Datasheet

1.DSP56301PW80B1.pdf

(124 pages)

Specifications of DSP56301PW80B1

Device Core Size

24b

Format

Fixed Point

Clock Freq (max)

80MHz

Mips

80

Device Input Clock Speed

80MHz

Ram Size

24KB

Program Memory Size

Not RequiredKB

Operating Supply Voltage (typ)

3.3V

Operating Supply Voltage (min)

3V

Operating Supply Voltage (max)

3.6V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

208

Package Type

TQFP

Lead Free Status / Rohs Status

Not Compliant

- Current page: 58 of 124

- Download datasheet (4Mb)

Specifications

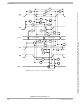

2.5.5.5 Asynchronous Bus Arbitrations Timings

2-32

Notes:

No.

250

251

BB assertion window from BG input deassertion

Delay from BB assertion to BG assertion

1.

2.

3.

4.

Note: Address lines A[0–23] hold their state after a read or write operation. AA[0–3] do not hold their

state after a read or write operation.

Bit 13 in the Operating Mode Register must be set to enter Asynchronous Arbitration mode.

Asynchronous Arbitration mode is recommended for operation at 100 MHz.

If Asynchronous Arbitration mode is active, none of the timings in Table 2-16 is required.

In order to guarantee timings 250, and 251, BG inputs must be asserted to different DSP56300 devices on the same bus in

the non-overlap manner shown in Figure 2-26.

CLKOUT

Figure 2-25.

RD, WR

AA[0–3]

A[0–23]

BG

BR

BB

Characteristics

Bus Release Timings Case 2 (BRT Bit in Operating Mode Register Set)

Table 2-17.

212

DSP56301 Technical Data, Rev. 10

4

Asynchronous Bus Arbitration Timing

4

213

223

Expression

2.5 × Tc + 5

2 × Tc + 5

214

221

Min

224

25

—

80 MHz

218

1,3

Max

25

—

Freescale Semiconductor

Min

—

25

100 MHz

219

Max

30

—

2

Unit

ns

ns

Related parts for DSP56301PW80B1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Dsp56301 24-bit Digital Signal Processor

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: