SAA7108E Philips Semiconductors, SAA7108E Datasheet

SAA7108E

Available stocks

Related parts for SAA7108E

SAA7108E Summary of contents

Page 1

... DATA SHEET SAA7108E; SAA7109E PC-CODEC Product specification File under Integrated Circuits, IC22 INTEGRATED CIRCUITS 2001 Dec 12 ...

Page 2

... INPUT/OUTPUT INTERFACES AND PORTS OF DIGITAL VIDEO DECODER PART 10.1 Analog terminals 10.2 Audio clock signals 2001 Dec 12 SAA7108E; SAA7109E 10.3 Clock and real-time synchronization signals 10.4 Video expansion port (X port) 10.5 Image port (I port) 10.6 Host port for 16-bit extension of video data I/O (H port) 10 ...

Page 3

... Up to 800 programmable underscan range Three Digital-to-Analog Converters (DACs MHz sample rate for CVBS (BLUE, C CVBS) and C (RED, C optional); all at 10-bit resolution 3 SAA7108E; SAA7109E (27 MHz data rate) Video scaler 1 / pixel or line, horizontally 64 POPCON applications or general VBI data decoding ...

Page 4

... System (CGMS) Macrovision Pay-per-View copy protection system rev. 7.01 and rev. 6.1 as option; this applies to SAA7108E only. The device is protected by USA patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. Use of the Macrovision anti-copy process in the device is licensed for non-commercial home use only ...

Page 5

... Philips Semiconductors PC-CODEC 3 GENERAL DESCRIPTION The SAA7108E; SAA7109E is a new multi-standard video decoder and encoder chip, offering high quality video input and TV output processing as required by PC-99 specifications. It enables hardware manufacturers to implement versatile video functions on a significantly reduced printed-circuit board area at very competitive costs ...

Page 6

... X port ANALOG VIDEO ACQUISITION AND DEMODULATOR VIDEO DECODER PART VIDEO ENCODER PART SCALER AND ENCODER PD INTERLACER Fig.1 Simplified block diagram. 6 Product specification SAA7108E; SAA7109E I port digital SCALER video output (IPD) CVBS, Y/C analog VIDEO video output RGB MHB903 ...

Page 7

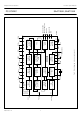

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 7 Product specification pagewidth full handbook, ...

Page 8

... Philips Semiconductors PC-CODEC , full pagewidth 2001 Dec 12 SAA7108E; SAA7109E MAPPING PIN PORT IMAGE 8 Product specification ...

Page 9

... O teletext request output or 13.5 MHz clock output of the crystal oscillator (encoder) S digital ground core (encoder) O BLUE CVBS output B 9 Product specification SAA7108E; SAA7109E DESCRIPTION -Y see Tables for pin see Tables for B R resistor connected to V SSAe ...

Page 10

... V digital supply voltage for peripheral cells (encoder) S 3.3 V digital supply voltage for core (decoder) not connected O multi-purpose vertical reference output with IPD output bus O general purpose output signal 0 with IPD output bus 10 Product specification SAA7108E; SAA7109E DESCRIPTION -Y see Tables for B R ...

Page 11

... XPD bus I/O MSB 3 of XPD bus I/O MSB 4 of XPD bus S 3.3 V digital supply voltage for core (decoder) I/O vertical reference for XPD bus 11 Product specification SAA7108E; SAA7109E DESCRIPTION -Y see Tables for see Tables for see Tables for B ...

Page 12

... BST (decoder); note 4 S analog ground (decoder) S analog ground (decoder) S analog ground (decoder) S analog ground (decoder) connected to substrate S 3.3 V analog supply voltage (decoder) S analog ground (decoder) S analog ground (decoder) I chip enable or reset input (with internal pull-up) 12 Product specification SAA7108E; SAA7109E DESCRIPTION ...

Page 13

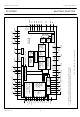

... I analog input 22 I analog input 21 I analog input 12 I differential analog input for channel 1; connect to ground via a capacitor I analog input SAA7108E G SAA7109E Fig.4 Pin configuration. 13 Product specification SAA7108E; SAA7109E DESCRIPTION MHB888 ...

Page 14

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 14 Product specification ...

Page 15

... NTSC M, PAL B/G and sub-standards R B are supported. The SAA7108E; SAA7109E can be directly connected video graphics controller with a maximum resolution of 800 600 frame rate. A programmable scaler scales the computer graphics picture so that it will fit into a standard TV screen with an adjustable underscan area ...

Page 16

... Philips Semiconductors PC-CODEC handbook, full pagewidth (dB ( (1) SCBW = 1. (2) SCBW = 0. handbook, halfpage (1) SCBW = 1. (2) SCBW = 0. 2001 Dec 12 ( Fig.5 Chrominance transfer characteristic (dB) 0 (1) ( 0.4 0.8 1.2 Fig.6 Chrominance transfer characteristic 2. 16 Product specification SAA7108E; SAA7109E (MHz) MBE735 1.6 f (MHz) MBE737 14 ...

Page 17

... CCRS1 = 0; CCRS0 = 1. (2) CCRS1 = 1; CCRS0 = 0. (3) CCRS1 = 1; CCRS0 = 1. (4) CCRS1 = 0; CCRS0 = 0. Fig.7 Luminance transfer characteristic 1 (excluding scaler). handbook, halfpage (1) CCRS1 = 0; CCRS0 = 0. Fig.8 Luminance transfer characteristic 2 (excluding scaler). 2001 Dec 12 (4) (2) (3) ( (dB) ( Product specification SAA7108E; SAA7109E MBE736 6 f (MHz) MGD672 14 f (MHz) ...

Page 18

... Philips Semiconductors PC-CODEC handbook, full pagewidth (dB Fig.9 Luminance transfer characteristic in RGB (excluding scaler). handbook, full pagewidth (dB Fig.10 Colour difference transfer characteristic in RGB (excluding scaler). 2001 Dec Product specification SAA7108E; SAA7109E MGB708 (MHz) MGB706 (MHz) ...

Page 19

... C-bus control The hot spot is the ‘tip’ of the pointer arrow. 19 Product specification SAA7108E; SAA7109E is being applied Mbyte/s data stream C-bus write access 3 bytes for the R, G and B LUT are 2 C-bus register as described in Table 5 ...

Page 20

... A special case is row 0 row 0 XINC = 0, this sets the scaling factor to 1. column 9 column 8 If the SAA7108E; SAA7109E input data is in accordance with “ITU-R BT.656” , the scaler enters another mode. ... ... In this event, XINC needs to be set to 2048 for a scaling row 0 row 0 factor of 1 ...

Page 21

... At each rising edge of the output signal (TTXRQ) a single teletext bit has to be provided after a programmable delay at input pin baseband signals, R TTX_SRES. 21 Product specification SAA7108E; SAA7109E and C ), and a standard dependent ELETEXT INSERTION AND ENCODING - SIMULTANEOUSLY WITH REAL ...

Page 22

... I C-bus status byte reflects whether a load is applied or not. If the SAA7108E; SAA7109E is required to drive a second (auxiliary) VGA monitor, the DACs receive the signal directly from the cursor insertion block. In this event, the DACs are clocked at the incoming PIXCLKI instead of the 27 MHz crystal clock used in the video encoder. ...

Page 23

... Alternatively, the device can be triggered by auxiliary codes in a ITU-R BT.656 data stream via PD7 to PD0. Only vertical frequencies of 50 and 60 Hz are allowed with the SAA7108E; SAA7109E. In slave mode not possible to lock the encoders colour carrier to the line frequency with the PHRES bits. ...

Page 24

... The (50 Hz) corresponding horizontal resolution is 620 pixels. Overscan is only possible with an input resolution of 800 settings are given on the last lines of the tables. 24 Product specification SAA7108E; SAA7109E HLEN is fulfilled. Values given by the InPix 1 XPIX XINC = ------------ - ...

Page 25

... PC-CODEC 8.18 Input levels and formats The SAA7108E; SAA7109E accepts digital Y, C “ITU-R BT.601” ; see Table 24. For C and CVBS outputs, deviating amplitudes of the colour difference signals can be compensated for by independent gain control setting, while gain for luminance is set to predefined values, distinguishable for 7.5 IRE set-up or without set-up ...

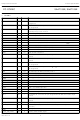

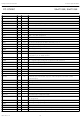

Page 26

... Product specification SAA7108E; SAA7109E 400, half anti-flicker filter YOFSO YOFSE YIWGTO 52 52 3668 56 56 3668 60 60 3668 64 64 3668 67 67 3668 50 50 3683 ...

Page 27

... Product specification SAA7108E; SAA7109E 400, no anti-flicker filter YOFSO YOFSE YIWGTO 52 52 4092 56 56 4092 60 60 4092 64 64 4092 68 68 4092 50 50 4091 ...

Page 28

... Product specification SAA7108E; SAA7109E 480, full anti-flicker filter YOFSO YOFSE YIWGTO 63 63 2948 67 67 2948 72 72 2948 77 77 2948 81 81 2948 60 60 2957 65 65 ...

Page 29

... Product specification SAA7108E; SAA7109E 480, half anti-flicker filter YOFSO YOFSE YIWGTO 63 63 3399 67 67 3399 72 72 3399 77 77 3399 81 81 3399 60 60 3412 ...

Page 30

... Product specification SAA7108E; SAA7109E 480, no anti-flicker filter YOFSO YOFSE YIWGTO 63 64 3849 68 69 3849 72 73 3849 77 78 3849 81 82 3849 60 61 3866 ...

Page 31

... Product specification SAA7108E; SAA7109E 600, full anti-flicker filter YOFSO YOFSE YIWGTO 79 79 2769 84 84 2769 90 90 2769 96 96 2769 102 102 2769 75 75 ...

Page 32

... Product specification SAA7108E; SAA7109E 600, half anti-flicker filter YOFSO YOFSE YIWGTO 79 79 3129 85 85 3129 91 91 3129 96 96 3129 102 102 3129 ...

Page 33

... Product specification SAA7108E; SAA7109E 600, no anti-flicker filter YOFSO YOFSE YIWGTO 79 80 3490 85 86 3490 91 92 3490 96 97 3490 102 103 3490 ...

Page 34

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 52 52 3347 55 55 3347 59 59 3347 62 62 3347 65 65 3347 50 50 3357 53 53 3357 57 57 3357 ...

Page 35

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 53 53 3996 56 56 3996 59 59 3996 62 62 3996 65 65 3996 51 51 4012 54 54 4012 ...

Page 36

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 53 53 4092 56 56 4092 59 59 4092 62 62 4092 65 65 4092 51 51 4092 54 54 4092 ...

Page 37

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 63 63 3131 67 67 3131 71 71 3131 74 74 3131 78 78 3131 61 61 3139 65 65 3139 69 69 3139 ...

Page 38

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 63 63 3673 67 67 3673 71 71 3673 75 75 3673 79 79 3673 61 61 3686 65 65 3686 ...

Page 39

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 64 64 4091 67 67 4091 71 71 4091 75 75 4091 79 79 4091 61 61 4091 65 65 4091 ...

Page 40

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 79 79 2915 84 84 2915 89 89 2915 93 93 2915 98 98 2915 77 77 2922 81 81 2922 86 ...

Page 41

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 80 80 3349 84 84 3349 89 89 3349 94 94 3349 98 98 3349 77 77 3359 82 ...

Page 42

... Product specification SAA7108E; SAA7109E YOFSO YOFSE YIWGTO 80 81 3783 84 85 3783 89 90 3783 94 95 3783 99 100 3783 77 78 3796 82 ...

Page 43

... Table 28 Pin assignment for input format 3 R3 8-BIT NON-INTERLACED PIN R0 G7/Y7 G6/Y6 PD7 G5/Y5 PD6 G4/Y4 PD5 PD4 PD3 PD2 PD1 PD0 43 Product specification SAA7108E; SAA7109E 5-BIT NON-INTERLACED RGB FALLING PIN CLOCK EDGE 5-BIT NON-INTERLACED RGB FALLING PIN CLOCK EDGE FALLING RISING FALLING CLOCK ...

Page 44

... Y4(1) R PD6 C 3(0) Y3(1) R PD5 C 2(0) Y2(1) R PD4 C 1(0) Y1(1) R PD3 C 0(0) Y0(1) R PD2 PD1 PD0 RISING CLOCK EDGE Product specification SAA7108E; SAA7109E RGB/C -Y FALLING PIN CLOCK EDGE G4/Y4 G3/Y3 G2/ G0/ RISING CLOCK EDGE R7 R6/C ...

Page 45

... Decoder 9.1.1 A NALOG INPUT PROCESSING The SAA7108E; SAA7109E offers six analog signal inputs, two analog main channels with source switch, clamp circuit, analog amplifier, anti-alias filter and video 9-bit CMOS ADC; see Fig.14. 9.1.2 A NALOG CONTROL CIRCUITS The anti-alias filters are adapted to the line-locked clock frequency via a filter control circuit. The characteristics are illustrated in Fig ...

Page 46

... The flow charts show more details of the AGC; see Figs 15 and 16. 2 C-bus) the static (1 V (p-p) 18/56 ) MGL065 46 Product specification SAA7108E; SAA7109E controlled analog input level ADC input level maximum range ...

Page 47

... Philips Semiconductors PC-CODEC dbook, full pagewidth 2001 Dec 12 SAA7108E; SAA7109E 47 Product specification ...

Page 48

... VBLK 1 0 HOLDG 254 248 1/F 1/L 1/LLC2 1/LLC2 GAIN ACCUMULATOR (18 BITS) ACTUAL GAIN VALUE 9-BIT (AGV AGV GAIN VALUE 9-BIT Fig.15 Gain flow chart. 48 Product specification SAA7108E; SAA7109E 9 DAC LUMA/CHROMA DECODER HSY 254 1/LLC2 0 0 HSY UPDATE FGV MHB531 ...

Page 49

... HSY = horizontal sync pulse. HCL = horizontal clamp pulse. 2001 Dec 12 ANALOG INPUT ADC 1 0 VBLK <- CLAMP GAIN -> HCL 0 0 SBOT NO CLAMP CLAMP GAIN Fig.16 Clamp and gain flow. 49 Product specification SAA7108E; SAA7109E 1 0 HSY WIPE slow GAIN GAIN fast GAIN MGC647 ...

Page 50

... Philips Semiconductors PC-CODEC 9.1.3 C HROMINANCE AND LUMINANCE PROCESSING 2001 Dec 12 SAA7108E; SAA7109E 50 Product specification pagewidth full handbook, ...

Page 51

... Figs 18 and 19. The SECAM processing (bypassed for QAM standards) contains the following blocks: 2001 Dec 12 SAA7108E; SAA7109E Baseband ‘bell’ filters to reconstruct the amplitude and phase equalized 0 and 90 FM signals Phase demodulator and differentiator (FM demodulation) De-emphasis filter to compensate the pre-emphasized ...

Page 52

... Product specification SAA7108E; SAA7109E MHB533 f (MHz) f (MHz) ...

Page 53

... Product specification SAA7108E; SAA7109E MHB534 f (MHz) f (MHz) ...

Page 54

... It should be noted that these frequency curves are only valid for Y comb disabled filter mode (YCOMB = 0). In comb filter mode the frequency response is flat. The centre frequency of the notch is automatically adapted to the chosen colour standard. 2001 Dec 12 SAA7108E; SAA7109E The interpolated C -C samples are multiplied by two B R time-multiplexed subcarrier signals from the subcarrier generation block 2 ...

Page 55

... Fig.20 Transfer characteristics of the luminance notch filter in 3.58 MHz mode (Y-comb filter disabled) at LUBW = 0. 2001 Dec 12 SAA7108E; SAA7109E (1) (2) (3) ...

Page 56

... Fig.21 Transfer characteristics of the luminance notch filter in 3.58 MHz mode (Y-comb filter disabled) at LUBW =1. 2001 Dec 12 SAA7108E; SAA7109E (1) (2) (3) ...

Page 57

... Fig.22 Transfer characteristics of the luminance notch filter in 4.43 MHz mode (Y-comb filter disabled) at LUBW = 0. 2001 Dec 12 SAA7108E; SAA7109E (1) (2) (3) ...

Page 58

... Fig.23 Transfer characteristics of the luminance notch filter in 4.43 MHz mode (Y-comb filter disabled) at LUBW = 1. 2001 Dec 12 SAA7108E; SAA7109E (1) (2) (3) ...

Page 59

... Dec 12 (1) (2) (3) (4) (5) (6) (7) (8) 0.5 1.0 1.5 2.0 2.5 (9) (10) (11) (12) (13) (14) (15) (16) 0.5 1.0 1.5 2.0 2.5 59 Product specification SAA7108E; SAA7109E 3.0 3.5 4.0 4.5 5.0 f (MHz) 3.0 3.5 4.0 4.5 5.0 f (MHz) MHB539 5.5 6.0 5.5 6.0 ...

Page 60

... C-bus bytes DBRI, DCON and DSAT 128 – + DBRI C C 128 128 – range for scaler input and X port output Product specification SAA7108E; SAA7109E 255 red 100% 240 212 red 75% colourless 128 C R -COMPONENT cyan 75% 44 cyan 100 MHB730 c. C output range. R ...

Page 61

... Fig.26 CVBS (raw data) range for scaler input, data slicer and X port output. 2001 Dec 12 255 white 199 black black shoulder 60 sync bottom – 128 + RAWO 61 SAA7108E; SAA7109E white LUMINANCE black shoulder = black SYNC 1 sync bottom MGD700 b. Sources not containing black level offset. Product specification ...

Page 62

... LLC8 (virtual) ZERO PHASE CROSS DETECTION DETECTION Fig.27 Block diagram of the clock generation circuit. INPUT supply voltages (below 2.7 V) will start the reset sequence; all outputs DDAd 62 Product specification SAA7108E; SAA7109E f (50 Hz (60 Hz). H CLOCK FREQUENCY (MHz) 24.576 or 32.110 27 13.5 6 ...

Page 63

... RES = reset output. 2001 Dec 12 POC V POC V DDD DDA ANALOG CLOCK PLL LLC POC LOGIC RESINT 20 to 200 s PLL-delay digital delay 1 ms Fig.28 Power-on control circuit. 63 Product specification SAA7108E; SAA7109E DIGITAL POC RES DELAY CLK0 896 LCC 128 LCC MHB331 ...

Page 64

... VOFF[8:0] = 03H for 50 Hz sources (with FOFF = 0) and VOFF[8:0] = 06H for 60 Hz sources (with FOFF = 1), to accommodate line number conventions as used for PAL, SECAM and NTSC standards; see Tables 34 to 37. DATA TYPE DECODER OUTPUT DATA FORMAT 64 Product specification SAA7108E; SAA7109E raw raw raw raw raw raw Y-C ...

Page 65

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 65 Product specification ...

Page 66

... Dec 12 625 624 311 312 (a) 1st field 312 313 314 315 316 311 312 313 311 (b) 2nd field RTS1 (PIN L10) XRH (PIN N2 Product specification SAA7108E; SAA7109E ... ... VSTA [ 8 15H 317 318 319 335 336 ... ... VSTA [ 8 15H MHB540 XRV (PIN L5 ...

Page 67

... Fig.30 Vertical timing diagram for 60 Hz/525 line systems. 2001 Dec (a) 1st field 264 265 266 267 268 (b) 2nd field RTS1 (PIN L10) XRH (PIN N2 Product specification SAA7108E; SAA7109E ... ... VSTA [ 8 011H 269 270 271 272 284 ... ... VSTA [ 8 011H XRV (PIN L5 285 22 MHB541 ...

Page 68

... ADC to expansion port: 140 1/LLC 720 2/LLC CREF CREF2 5 2/LLC 108 0 720 2/LLC CREF CREF2 1 2/LLC 107 0 Fig.31 Horizontal timing diagram (50/60 Hz). 68 Product specification SAA7108E; SAA7109E burst sync clipped 12 2/LLC 144 2/LLC 2 2/LLC 107 16 2/LLC 138 2/LLC 2 2/LLC 106 MHB542 ...

Page 69

... The access/bandwidth requirements to the VGA frame buffer are reduced significantly. The high performance video scaler in the SAA7108E; SAA7109E has the following major blocks. Acquisition control (horizontal and vertical timer) and task handling (the region/field/frame based processing) ...

Page 70

... The scaler gets corresponding field ID information directly from the SAA7108E; SAA7109E decoder path. The FID flag is used to determine whether the first or second field of a frame is going to be processed within the scaler, and it is also used as trigger conditions for the task handling (see bits STRC[1:0] 90H[1:0]) ...

Page 71

... A STRC[2: YO[11:0] = 310 and task B STRC[2: YO[11:0] = 310 results in an output field rate of After power-on or software reset (via SWRST[88H[5]]) task B gets priority over task A. 71 Product specification SAA7108E; SAA7109E DESCRIPTION 50 Hz). 3 ...

Page 72

... Section 9.3.3. 2001 Dec 12 SAA7108E; SAA7109E When OFIDC = 0, the scalers input field ID is available as output field ID on bit D6 of SAV and EAV, and respectively on pin IGP0 (IGP1), if the FID output is selected. ...

Page 73

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 73 Product specification ...

Page 74

... Together the prescaler and fine scaler form the horizontal scaler of the SAA7108E; SAA7109E. Using the accumulation length function of the prescaler (XACL[5:0] A1H[5:0]), application and destination dependent (e ...

Page 75

... Fade-in and fade-out of the filters is achieved by copying an original source sample each as first and last pixel after prescaling. Figs 32 and 33 show the frequency characteristics of the selectable FIR filters. XDCG[2:0] 2 --------------------------------- - DC gain 64 XC2_1). LUMINANCE FILTER COEFFICIENTS bypassed 1.75 4.5 1. Product specification SAA7108E; SAA7109E CHROMINANCE COEFFICIENTS bypassed ...

Page 76

... Dec 12 (3) 0.05 0.1 0.15 0.2 0.25 Fig.32 Luminance prefilter characteristic. (2) (3) 0.025 0.05 0.075 0.1 Fig.33 Chrominance prefilter characteristic. 76 Product specification SAA7108E; SAA7109E (1) (2) 0.3 0.35 0.4 0.45 f_sig/f_clock (1) 0.125 0.15 0.175 0.2 0.225 f_sig/f_clock MHB543 0.5 MHB544 ...

Page 77

... Fig.35 Examples for prescaler filter characteristics: setting XC2_1 =1. 2001 Dec 12 (5) (4) (3) 0.05 0.1 0.15 0.2 (1) (2) (6) (5) (4) (3) 0.05 0.1 0.15 0.2 0.25 77 Product specification SAA7108E; SAA7109E (2) (1) 0.25 0.3 0.35 0.4 f_sig/f_clock 0. 0.33 0.3 0.35 0.4 0.45 f_sig/f_clock MHB545 0.45 0.5 MHB546 0.5 ...

Page 78

... Philips Semiconductors PC-CODEC Table 41 Example of XACL[5:0] usage PRESCALE XPSC FOR LOWER BANDWIDTH RATIO [5:0] XACL[5: Note 1. Resulting FIR function. 2001 Dec 12 RECOMMENDED VALUES REQUIREMENTS XC2_1 XDCG[2:0] XACL[ Product specification SAA7108E; SAA7109E FOR HIGHER BANDWIDTH REQUIREMENTS XC2_1 XDCG[ FIR PREFILTER PFY[1:0]/ PFUV[1: ...

Page 79

... V ERTICAL SCALING The vertical scaler of the SAA7108E; SAA7109E decoder part consists of a line FIFO buffer for line repetition and the vertical scaler block, which implements the vertical scaling on the input data stream in 2 different operational modes ...

Page 80

... ID is the reference for the back-end operation, then it is UP-LO = UP-UP and LO-UP = LO-LO and the skipped; this case is given in Table 43. The SAA7108E; SAA7109E supports 4 phase offset registers per task and component (luminance and chrominance). The value of 20H represents a phase shift of one line. ...

Page 81

... Fig.36 Basic problem of interlaced vertical scaling (example: downscale 2001 Dec 12 scaled output, no phase offset field 1 field 2 field 1 mismatched vertical line distances 81 Product specification SAA7108E; SAA7109E scaled output, with phase offset field 2 correct scale dependent position MHB547 ...

Page 82

... UP-UP case LO- input line shift = scale increment offset = 0 USED ABBREVIATION UP-UP UP-LO LO-UP LO-LO 82 Product specification SAA7108E; SAA7109E field 1 field 2 case UP-LO case LO-UP MHB548 1 YSCY[15: scale increment ------------------------------ - + 2 64 YSCY[15:0] = ------------------------------ - with field 5 EQUATION FOR PHASE OFFSET CALCULATION (DECIMAL VALUES) ...

Page 83

... Case 3: OFIDC[90H[6 task status bit as output ID; back-end interprets output field ID at logic 1 as upper output lines. 9.4 VBI-data decoder and capture (subaddresses 40H to 7FH) The SAA7108E; SAA7109E contains a versatile VBI data decoder. The implementation and programming model accords to the VBI data slicer the built-in multimedia video data acquisition circuit of the SAA5284. ...

Page 84

... Start and end of vertical active video range Start and end of active video line Data qualifier or gated clock Actually activated programming page (if CONLH is used) Threshold controlled FIFO filling flags (empty, full, filled) Sliced data marker. 2001 Dec 12 SAA7108E; SAA7109E DATA RATE FRAMING CODE (Mbits/s) 6.9375 27H 0.500 001 ...

Page 85

... Additionally the output formatter limits the amplitude range of the video data (controlled by ILLV[85H[5]]); see Table 47. BYTE SEQUENCE FOR 8-BIT OUTPUT MODES EXPLANATION SUPPRESSED CODES (HEXADECIMAL VALUE) HEXADECIMAL VALUE Product specification SAA7108E; SAA7109E Y10 Y11 LOWER RANGE UPPER RANGE Y12 Y13 FF ...

Page 86

... FIFO does not need to buffer any output pixel, the text data is inserted after the end of a scaled video line, normally during the video blanking interval. 86 Product specification SAA7108E; SAA7109E V ( IDEO AND TEXT ARBITRATION SUBADDRESS 86H) ...

Page 87

... Table 48 shows the relevant and supported SAV and EAV coding. SAV/EAV CODES ON I PORT (2) MSB OF SAV/EAV BYTE = 0 MSB FIELD FIELD MSB = CONLH[90H[7]]; task B MSB = 1; DID[5:0] 5DH[5:0] = 3FH 87 Product specification SAA7108E; SAA7109E (1) (HEX) (2) OF SAV/EAV BYTE = 1 FIELD FIELD MSB = CONLH[C0H[7]]. COMMENT HREF = active; VREF = active HREF = inactive; VREF = active HREF = active ...

Page 88

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 88 Product specification ...

Page 89

... V NEP EP D5[5EH] D4[5EH] D3[5EH] D2[5EH] D1[5EH] D0[5EH] (2) NEP EP DC5 (9) (3) (10) OP FID LN8 LN7 (10) (10) OP LN2 LN1 LN0 CS6 CS6 CS5 OP 0 CNT5 CNT4 89 Product specification SAA7108E; SAA7109E ( FID ( ( DC4 DC3 DC2 DC1 (10) (10) (10) LN6 LN5 LN4 (10) (11) (11) DT3 DT2 ...

Page 90

... PC-CODEC 9.6 Audio clock generation (subaddresses 30H to 3FH) The SAA7108E; SAA7109E incorporates the generation of a field-locked audio clock auxiliary function for video capture. An audio sample clock, that is locked to the field frequency, ensures that there is always the same predefined number of audio samples associated with a field set of fields ...

Page 91

... AMXCLK, ASCLK edges triggered by falling edge of AMXCLK 1: do not invert AMXCLK, ASCLK edges triggered by rising edge of AMXCLK 2001 Dec 12 f AMXCLK f = ------------------------------------- - ASCLK SDIV ASCLK f = -------------------------- - ALRCLK LRDIV 2 SDIV DECIMAL HEX DESCRIPTION 91 Product specification SAA7108E; SAA7109E f AMXCLK SDIV[5:0] ------------------- - 1 = – ASCLK f ASCLK LRDIV[5:0] = ---------------------- - 2f ALRCLK LRDIV ALRCLK (kHz) DECIMAL 44 HEX ...

Page 92

... Audio clock signals The SAA7108E; SAA7109E also synchronizes the audio clock and sampling rate to the video frame rate, via a very slow PLL. This ensures that the multimedia capture and compression processes always gather the same predefined number of samples per video frame. ...

Page 93

... RTS pins. The signals are always available (output) and reflect the synchronization operation of the decoder part in the SAA7108E; SAA7109E. The function of the RTS1 and RTS0 pins can be defined by bits RTSE1[3:0] 12H[7:4] and RTSE0[3:0] 12H[3:0]; see Table 56. ...

Page 94

... XCODE[92H[3]]). The input/output direction is switched for complete fields only DESCRIPTION - serial input data or luminance part input Product specification SAA7108E; SAA7109E BIT OFTS[2:0] 13H[2:0], 91H[7:0] and C1H[7:0] XCKS[92H[0]] XRQT[83H[2]] XRHS[13H[6]], XFDH[92H[6]] and XDH[92H[2]] XRVS[1:0] 13H[5:4], XFDV[92H[7]] and XDV[1:0] 92H[5:4] XPE[1:0] 83H[1:0] ...

Page 95

... The V bit can be generated in two different ways (see Tables 60 and 61) controlled via OFTS1 and OFTS0; see Table 169. F and V bits change synchronously with the EAV code. 720 PIXELS Y DATA ... Product specification SAA7108E; SAA7109E TIMING (2) REFERENCE (1) CODE (HEX) 718 Y719 EAV 80 10 ... BLANKING PERIOD ...

Page 96

... OFTS[2:0] = 000 (ITU 656 Product specification SAA7108E; SAA7109E BIT 4 BIT 3 BIT 2 (H) (P3) (P2) reserved; evaluation not recommended (protection bits according to ITU 656) V OFTS[2:0] = 001 according to selected VGATE position type via VSTA and VSTO (subaddresses 15H to 17H); see Tables 171 to 173 ...

Page 97

... IDQ pin can be programmed to function as a gated clock output (bit ICKS2[80H[2]]). 2001 Dec 12 SAA7108E; SAA7109E The data formats at the image port are defined in Dwords of 32 bits (4 bytes), such as the related FIFO structures. However, the physical data stream at the image port is only 16-bit or 8-bit wide ...

Page 98

... Philips Semiconductors PC-CODEC The following deviations from “ITU 656 recommendation” are implemented at the SAA7108E; SAA7109Es image port interface: SAV and EAV codes are only present in those lines, where data transferred, i.e. active video lines, or VBI raw samples, no codes for empty lines ...

Page 99

... XCLK may by a gated clock (XCLK AND external XDQ). Remark: All timings illustrated are given for an uninterrupted output stream (no handshake with the external hardware SAV Product specification SAA7108E; SAA7109E BIT IPE[1:0] 87H[1:0], ITRI[8FH[6]] and I8_16[93H[6]] X PORT INPUT TIMING MHB550 ...

Page 100

... Fig.40 Output timing at the I port for serial 8-bit data at start of a line (ICODE = 0). ICLK IDQ IPD [ 7 IGPH Fig.41 Output timing at the I port for serial 8-bit data at end of a line (ICODE = 1). 2001 Dec 100 Product specification SAA7108E; SAA7109E MHB551 EAV 00 MHB552 ...

Page 101

... FF 00 HPD [ 7 SAV IGPH Fig.43 Output timing for 16-bit data output via the I and H port with codes (ICODE = 1), timing is like 8-bit output, but packages of 2 bytes per valid cycle. 2001 Dec 101 Product specification SAA7108E; SAA7109E MHB553 00 00 EAV 00 MHB554 ...

Page 102

... IGP0 or IGP1 Fig.45 Output timing for sliced VBI data in 8-bit serial output mode (dotted graphs for SAV/EAV mode). 2001 Dec 12 Fig.44 Horizontal and vertical gate output timing. FF DID SDID SAV 102 Product specification SAA7108E; SAA7109E MHB555 EAV MHB733 ...

Page 103

... Philips Semiconductors PC-CODEC 11 BOUNDARY SCAN TEST The SAA7108E; SAA7109E has built-in logic and 2 times 5 dedicated pins to support boundary scan testing, separately for the encoder and decoder part, which allows board testing without special hardware (nails). The SAA7108E; SAA7109E follows the “IEEE Std. 1149.1 - Standard Test Access Port and Boundary-Scan Architecture” ...

Page 104

... MSB 0111000100000011 nnnn (0111000100010100) 4-bit 16-bit part number version code Fig.46 32 bits of identification code. 104 Product specification SAA7108E; SAA7109E LSB 1 0 TDOe 1 00000010101 (or TDOd) 11-bit manufacturer identification LSB 1 0 TDOe 00000010101 1 (or TDOd) 11-bit manufacturer ...

Page 105

... THERMAL CHARACTERISTICS SYMBOL PARAMETER R thermal resistance from junction to ambient th(j-a) 2001 Dec 12 CONDITIONS outputs in 3-state; note 2 outputs active and V SSA(n) SSD(n) note 3 CONDITIONS in free air 105 Product specification SAA7108E; SAA7109E MIN. MAX. UNIT 0.5 +4.6 V 0.5 +4.6 V (1) 0 0.5 V DDA 0 0.5 ...

Page 106

... V; note 2 DDD clocks data I/Os at high-impedance LOW or HIGH during acknowledge note 3 note 4 note 3 PIXCLK output CLKO2 note 3 note 3 106 Product specification SAA7108E; SAA7109E MIN. TYP. MAX. 3.15 3.3 3.45 3.0 3.3 3.6 1 107 120 0.5 +0.8 2 0.3 V DDD 0.4 2.4 ...

Page 107

... C-bus bit DOWND = 1. 3. The data is for both input and output direction. 4. This parameter is arbitrary, if PIXCLKI is looped through the VGC internal oscillator is used, crystal deviation of nominal frequency is directly proportional to the deviation of subcarrier frequency and line/field frequency. 2001 Dec 12 SAA7108E; SAA7109E CONDITIONS MIN. note ...

Page 108

... for normal video levels 1 V (p-p termination 27/47 and AC coupling required; coupling capacitor = 22 nF clamping current off 200 f < 5 MHz 12.8 108 Product specification SAA7108E; SAA7109E MIN. TYP. MAX. 3.3 3.6 90 300 3.3 3. 150 240 450 540 ...

Page 109

... SDAd sink current pin LLC pin LLC2 / LLC L 0 0.2 V DDD V 0 0.2 V DDD measured at 1 field 60 Hz field 109 Product specification SAA7108E; SAA7109E MIN. TYP. MAX. 1 0.5 +0.3V DDD 0. 0.5 DDD DDD 0.3 +0.8 2 0.3 DDD 0.3 +0.8 2.0 5 ...

Page 110

... Data and control signal input timing X port, related to XCLK input t input data set-up time SU;DAT t input data hold time HD;DAT 2001 Dec 12 CONDITIONS PAL BGHI NTSC M PAL M PAL N 3rd-harmonic 3rd-harmonic /t LLC 110 Product specification SAA7108E; SAA7109E MIN. TYP. MAX. 4433619 3579545 3575612 3582056 400 32. ...

Page 111

... The effects of rise and fall times are included in the calculation of t drawings and conditions illustrated in Fig.51. 3. The crystal oscillator drive level is 0.28 mW (typ.). 2001 Dec 12 CONDITIONS 0.6 to 2.6 V 2 ICLKL 0.6 to 2.6 V 2 111 Product specification SAA7108E; SAA7109E MIN. TYP. MAX ...

Page 112

... Dec 12 T PIXCLK t HIGH HD;DAT t HD;DAT t SU;DAT t o(d) t o(h) Fig.47 Input/output timing specification. XOFS IDEL XPIX HLEN Fig.48 Horizontal input timing. 112 Product specification SAA7108E; SAA7109E 2.4 V 1 2.0 V 1 SU;DAT 2.0 V 0.8 V 2.4 V 0.4 V MHB904 MHB905 ...

Page 113

... Philips Semiconductors PC-CODEC handbook, full pagewidth HSVGC VSVGC CBO 2001 Dec 12 YOFS YPIX Fig.49 Vertical input timing. 113 Product specification SAA7108E; SAA7109E MHB906 ...

Page 114

... TTXEVE) can be used for teletext insertion essential to note that the two pins used for teletext insertion must be configured for this purpose by the correct Fig.50 Teletext timing. 114 Product specification SAA7108E; SAA7109E is the internally used insertion window for i(TTXW) 2 C-bus register settings. t i(TTXW MHB891 ...

Page 115

... ICLK input Fig.51 Data input/output timing diagram (X port, RT port and I port). 2001 Dec XCLKH HD;DAT not valid t SU;DAT t o(d) t OHD;DAT t X(I)CLKL t X(I)CLKH t f 115 Product specification SAA7108E; SAA7109E 2.4 V 1 2 HD;DAT 2.0 V 0.8 V 2.4 V 0.6 V 2.6 V 1 ...

Page 116

... V DD (XL8) C56 C59 C57 C58 C61 100 100 100 100 100 DGND DXGND AGND Fig.52 Application circuit (decoder part). 116 SAA7108E; SAA7109E V DD (ID11 (IF11 (IJ4 (IJ11 (IL4 (IL11 (XL8) R27 0 L12 R28 0 SDAd M11 SCLd K2 XPD7 XPD7 K3 XPD6 XPD6 L1 ...

Page 117

... PC-CODEC book, full pagewidth DDAe V D9 DDAe V C9 DDAe V B9 DDAe V B6 DDAe V A10 DDEe V F4 DDIe V D4 DDXe V D6 2001 Dec 12 CBNO HSIO TTXRQ 117 Product specification SAA7108E; SAA7109E SSAe V B8 SSEe V E4 SSIe V D5 SSIe V C5 SSXe V A8 ...

Page 118

... With fundamental quartz and restricted drive level. When P is too high, a resistance R Note: The decreased crystal amplitude results in a lower drive level but on the other hand the jitter performance will decrease. Fig.54 Oscillator application for decoder part. 118 SAA7108E; SAA7109E SAA7108E SAA7109E P3 P2 XTALOd XTALId 32 ...

Page 119

... R s Note: The decreased crystal amplitude results in a lower drive level but on the other hand the jitter performance will decrease. Fig.55 Oscillator application for encoder part. 119 Product specification SAA7108E; SAA7109E SAA7108E SAA7109E A5 A6 XTALIe XTALOe 27.00 MHz ...

Page 120

... Be careful of hidden layout capacitors around the crystal application. Use serial resistors in clock, sync and data lines, to avoid clock or data reflection effects and to soften data energy. 120 Product specification SAA7108E; SAA7109E RGB, BLACK-TO-WHITE see Table 83 876 e.g. R DAC = G DAC = B DAC = 0BH 0.70 V (p-p) ...

Page 121

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 121 Product specification ...

Page 122

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 122 Product specification ...

Page 123

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 123 Product specification ...

Page 124

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 124 Product specification ...

Page 125

... X is the read/write control bit logic 0 is order to write logic 1 is order to read more than 1 byte of DATA is transmitted, then auto-increment of the subaddress is performed. 2001 Dec 12 A DATA 0 RAM ADDRESS A DATA 0 A DATA DESCRIPTION 125 Product specification SAA7108E; SAA7109E A -------- DATA n A -------- DATA n A DATA 0G A DATA 0B A DATA 0 Am -------- DATA n ...

Page 126

... DAC output voltage, should be set to 70 2001 Dec 12 DESCRIPTION DESCRIPTION 1.240 V at 37.5 nominal for full-scale conversion 1.240 V at 37.5 nominal for full-scale conversion 1.240 V at 37.5 nominal for full-scale conversion DESCRIPTION 126 Product specification SAA7108E; SAA7109E GAIN (%) ...

Page 127

... G1 tied LOW DESCRIPTION default after reset a HIGH impulse resets synchronization of the encoder (first field, first line) PAL (1DH); default after reset if strapping pin G1 tied HIGH NTSC (1DH); default after reset if strapping pin G1 tied LOW 127 Product specification SAA7108E; SAA7109E REMARKS REMARKS ...

Page 128

... Table 83 Subaddresses 38H and 39H DATA BYTE GY4 to GY0 Gain luminance of RGB (C Suggested nominal value = 0, depending on external application. GCD4 to GCD0 Gain colour difference of RGB (C Suggested nominal value = 0, depending on external application. 2001 Dec 12 SAA7108E; SAA7109E DESCRIPTION DESCRIPTION DESCRIPTION , Y and C ) output, ranging from ( and C ...

Page 129

... VPS14 fourteenth byte of video programming system data 2001 Dec 12 DESCRIPTION to RGB dematrix is active; default after reset R to RGB dematrix is bypassed R DESCRIPTION DESCRIPTION 129 Product specification SAA7108E; SAA7109E REMARKS in line 16; LSB first; all other bytes are not relevant for VPS ...

Page 130

... IRE; recommended value: BLCKL = 51 (33H) note 2 BLCKL = 0; note 2 output black level = 27 IRE BLCKL = 63 (3FH); note 2 output black level = 47 IRE 2/6.29 + 28.9. 2/6.18 + 26.5. 130 Product specification SAA7108E; SAA7109E RESULT REMARKS nominal to +2.16 nominal nominal to +2.04 nominal REMARKS nominal to +1.55 nominal nominal to +1 ...

Page 131

... DESCRIPTION DESCRIPTION DESCRIPTION black 100 IRE black 92.5 IRE including 7.5 IRE set-up of black 131 Product specification SAA7108E; SAA7109E REMARKS recommended value: BLNNL = 46 (2EH) output blanking level = 25 IRE output blanking level = 45 IRE recommended value: BLNNL = 53 (35H) output blanking level = 26 IRE ...

Page 132

... FSC = 569408543 (21F07C1FH). = 1728 FSC = 705268427 (2A098ACBH). llc DESCRIPTION DESCRIPTION 132 Product specification SAA7108E; SAA7109E REMARKS recommended value: BSTA = 63 (3FH) nominal recommended value: BSTA = 45 (2DH) nominal recommended value: BSTA = 67 (43H) nominal recommended value: BSTA = 47 (2FH); default after ...

Page 133

... Hz, 262.5 lines/field at 60 Hz; default after reset 0 1 non-interlaced 312 lines/field at 50 Hz, 262 lines/field non-interlaced 313 lines/field at 50 Hz, 263 lines/field non-interlaced 313 lines/field at 50 Hz, 263 lines/field 2001 Dec 12 SAA7108E; SAA7109E DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION 133 Product specification ...

Page 134

... RGB output from 0 XTAL clocks to 31 XTAL clocks 2001 Dec 12 DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION 134 Product specification SAA7108E; SAA7109E REMARKS TTXHS = 42H; is default after reset if strapped to PAL TTXHS = 54H; is default after reset if strapped to NTSC REMARKS minimum value: TTXHD = 2; is default after reset ...

Page 135

... TTXOVS/TTXOVE and TTXEVS/TTXEVE 2001 Dec 12 DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION 135 Product specification SAA7108E; SAA7109E REMARKS TTXOVS = 05H; is default after reset if strapped to PAL TTXOVS = 06H; is default after reset if strapped to NTSC TTXOVE = 16H; is default after reset if strapped to PAL TTXOVE = 10H; is default after ...

Page 136

... FSVGC accepted in slave mode PCBN 0 normal polarity of CBO signal (HIGH during active video) 1 inverted polarity of CBO signal (LOW during active video) SLAVE 0 the SAA7108E; SAA7109E is timing master to the graphics controller 1 the SAA7108E; SAA7109E is timing slave to the graphics controller 2001 Dec 12 DESCRIPTION MHz nominal, e ...

Page 137

... HSL 0 normal trigger event handling of the horizontal state machine, if the SAA7108E; SAA7109E is slave to HSVGC input 1 trigger event for horizontal state machine is shifted 128 PIXCLKs in advance, adapted to a late HSVGC in slave mode Table 122 Subaddress 97H ...

Page 138

... Table 131 Subaddresses A2H to A4H DATA BYTE BCY, BCU luminance and colour difference portion of border colour in underscan area and BCV 2001 Dec 12 SAA7108E; SAA7109E DESCRIPTION DESCRIPTION number of output pixels ------------------------------------------------------------- - line XINC = ------------------------------------------------------------- - ...

Page 139

... Table 137 Subaddresses FBH and FCH DATA BYTE YCP vertical cursor position Table 138 Subaddress FCH DATA BYTE YHS vertical hot spot of cursor 2001 Dec 12 SAA7108E; SAA7109E DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION 139 Product specification ...

Page 140

... In subaddresses 5BH, 5CH, 5DH, 5EH and 62H all IRE values are rounded up. 2001 Dec 12 DESCRIPTION -Y-C matrix is active R B -Y-C matrix is bypassed R B DESCRIPTION DESCRIPTION 140 Product specification SAA7108E; SAA7109E -Y -Y -Y-C (ITU-R BT.656, 27 MHz clock -Y-C (special bit ordering ...

Page 141

... O_E 1 during even field 0 during odd field Table 144 Subaddress 1CH DATA BYTE CID chip ID of SAA7108E = 02H; chip ID of SAA7109E = 03H Table 145 Subaddress 80H LOGIC DATA BYTE LEVEL OVFL 0 no FIFO overflow 1 FIFO overflow has occurred; this bit is reset after this subaddress has been read ...

Page 142

... P STOP condition X read/write control bit (LSB slave address order to write (the circuit is slave receiver order to read (the circuit is slave transmitter) Notes 1. The SAA7108E; SAA7109E supports the ‘fast mode’ pin RTCO strapped to V DDD 2001 Dec 12 ACK-s SUBADDRESS a. Write procedure. ...

Page 143

... BFH task A definition C0H to EFH task B definition 2001 Dec 12 DESCRIPTION 143 Product specification SAA7108E; SAA7109E ACCESS (READ/WRITE) read only read and write read and write read only read and write read and write read only ...

Page 144

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 144 Product specification ...

Page 145

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 145 Product specification ...

Page 146

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 146 Product specification ...

Page 147

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 147 Product specification ...

Page 148

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 148 Product specification ...

Page 149

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 149 Product specification ...

Page 150

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 150 Product specification ...

Page 151

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 151 Product specification ...

Page 152

... Y gain) from AI21 (pin P10); note 1; see Fig.65 1001 Mode 9: Y (automatic gain) from AI12 (pin P11 (gain adapted to Y gain) from AI22 (pin P9); note 1; see Fig.66 1111 Modes 10 to 15: reserved 2 C-bus bit BYPS (subaddress 09H, bit 7) should be set to logic 1 152 Product specification SAA7108E; SAA7109E FUNCTION ...

Page 153

... AI11 MHB561 Fig.60 Mode 3; CVBS (automatic gain). AI24 AI23 AI22 CHROMA AI21 LUMA AI12 AI11 MHB563 Fig.62 Mode 5; CVBS (automatic gain). 153 Product specification SAA7108E; SAA7109E AD2 CHROMA LUMA AD1 MHB560 AD2 CHROMA LUMA AD1 MHB562 AD2 CHROMA LUMA AD1 ...

Page 154

... AI21 LUMA AI12 AI11 MHB567 2 I C-bus bit BYPS (subaddress 09H, bit 7) should be set to logic 1 (full luminance bandwidth). Fig.66 Mode (gain channel 2 adapted to Y gain). 154 Product specification SAA7108E; SAA7109E AD2 CHROMA LUMA AD1 MHB566 AD2 CHROMA LUMA AD1 MHB568 ...

Page 155

... GAI[17:10] and GAI[27:20] GAI28 GAI18 CONTROL BITS GAI17 GAI16 GAI15 CONTROL BITS GAI27 GAI26 GAI25 155 Product specification SAA7108E; SAA7109E FUNCTION see Table 154 see Table 153 GAI14 GAI13 GAI12 GAI11 GAI24 GAI23 GAI22 GAI21 GAI10 ...

Page 156

... CONTROL BITS HSS7 HSS6 HSS5 forbidden (outside available central counter range forbidden (outside available central counter range) 156 Product specification SAA7108E; SAA7109E HSB4 HSB3 HSB2 HSS4 HSS3 HSS2 HSB1 HSB0 0 ...

Page 157

... ODD/EVEN signal toggles fieldwise even if source is non-interlaced HTC[1: mode, recommended for poor quality TV signals only; do not use for new applications 01 VTR mode, recommended if a deflection control circuit is directly connected to the SAA7108E; SAA7109E 10 reserved 11 fast locking mode; recommended setting HPLL 0 PLL closed 1 PLL open ...

Page 158

... MHz; notch at 3.4 MHz 1110 low-pass filter 1.9 MHz; notch at 3.0 MHz 1111 low-pass filter 1.7 MHz; notch at 2.5 MHz CONTROL BITS DBRI6 DBRI5 DBRI4 158 Product specification SAA7108E; SAA7109E FUNCTION higher luminance bandwidth) smaller luminance bandwidth) DBRI3 DBRI2 DBRI1 DBRI0 ...

Page 159

... Table 162 Chrominance hue control: 0DH[7:0] HUE PHASE (DEG) HUEC7 +178.6... ...0... ... 180 2001 Dec 12 CONTROL BITS DCON6 DCON5 DCON4 CONTROL BITS DSAT6 DSAT5 DSAT4 CONTROL BITS HUEC6 HUEC5 HUEC4 159 Product specification SAA7108E; SAA7109E DCON3 DCON2 DCON1 DSAT3 DSAT2 DSAT1 HUEC3 HUEC2 HUEC1 DCON0 ...

Page 160

... SECAM standard CGAIN[6:0] 000 0000 minimum gain (0.5) 010 0100 nominal gain (1.125) 111 1111 maximum gain (7.5) 160 Product specification SAA7108E; SAA7109E FUNCTION 60 Hz/525 LINES NTSC M (3.58 MHz) PAL 4.43 (60 Hz) NTSC 4.43 (60 Hz) PAL M (3.58 MHz) NTSC-Japan (3 ...

Page 161

... D[5:4] fine position of HS (steps in 2/LLC) D3 polarity of RTS0 output signal D[2:0] luminance delay compensation (steps in 2/LLC) YDEL[2:0] 2001 Dec 12 SYMBOL Y component OFFU[1:0] Y component OFFV[1:0] CHBW LCBW[2:0] SYMBOL COLO RTP1 HDEL[1:0] RTP0 161 Product specification SAA7108E; SAA7109E VALUE FUNCTION 00 0 LSB 1 01 LSB LSB LSB LSB ...

Page 162

... FID; position programmable via VSTA[8:0] 17H[0] 15H[7:0]; see vertical timing diagrams Figs 29 and 30 Note 1. Function selectable via HLSEL[13H[3]]: a) HLSEL = standard horizontal lock indicator. b) HLSEL = fast horizontal lock indicator (use is not recommended for sources with unstable timebase e.g. VCRs). 2001 Dec 12 SAA7108E; SAA7109E RTSE03 RTSE02 RTSE01 RTSE00 ...

Page 163

... FID; position programmable via VSTA[8:0] 17H[0] 15H[7:0]; see vertical timing diagrams Figs 29 and 30 Note 1. Function selectable via HLSEL[13H[3]]: a) HLSEL = standard horizontal lock indicator. b) HLSEL = fast horizontal lock indicator (use is not recommended for sources with unstable timebase e.g. VCRs). 2001 Dec 12 SAA7108E; SAA7109E RTSE13 RTSE12 RTSE11 RTSE10 ...

Page 164

... ADCs are selected AD2 is output at CREF = 1 and AD1 is output at CREF = 0 110 reserved 111 multiplexed ADC MSB/LSB bypass dependent on mode settings; only one ADC should be selected at a time; ADx8 to ADx1 are outputs at CREF = 1 and ADx7 to ADx0 are outputs at CREF = 0 164 Product specification SAA7108E; SAA7109E FUNCTION ...

Page 165

... AOUT connected to internal test point 1 01 AOUT connected to input AD1 10 AOUT connected to input AD2 11 AOUT connected to internal test point 2 XTOUTE 0 pin P4 (XTOUTd) 3-stated 1 pin P4 (XTOUTd) enabled OLDSB 0 standard 1 backward compatibility to SAA7112 APCK[1:0] 00 application dependent 165 Product specification SAA7108E; SAA7109E FUNCTION ...

Page 166

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 166 Product specification ...

Page 167

... Philips Semiconductors PC-CODEC 2001 Dec 12 SAA7108E; SAA7109E 167 Product specification ...

Page 168

... VGATE position according to Tables 171 and 172 1 VGATE occurs one line earlier during field 2 VSTO8 VSTA8 CONTROL BITS RAWG6 RAWG5 RAWG4 CONTROL BITS RAWO6 RAWO5 RAWO4 168 Product specification SAA7108E; SAA7109E FUNCTION see Table 172 see Table 171 RAWG3 RAWG2 RAWG1 RAWO3 RAWO2 RAWO1 RAWG0 ...

Page 169

... CONTROL BIT INTL HLVLN HLCK FIDT GLIMT GLIMB WIPA COPRO SLTCA RDCAP CODE CONTROL BITS ACPF6 ACPF5 ACPF4 ACPF14 ACPF13 ACPF12 169 Product specification SAA7108E; SAA7109E OLDSB VALUE FUNCTION 14H[2] 0 non-interlaced 1 interlaced 0 0 both loops locked 1 unlocked 1 0 locked 1 unlocked ...

Page 170

... Hamming check FCE 0 one framing code error allowed 1 no framing code errors allowed HUNT_N 0 amplitude searching active (default) 1 amplitude searching stopped 170 Product specification SAA7108E; SAA7109E ACNI3 ACNI2 ACNI1 ACNI11 ACNI10 ACNI9 ACNI19 ACNI18 ACNI17 SDIV3 SDIV2 SDIV1 LRDIV3 ...

Page 171

... CONTROL BITS 5BH[2:0] HOFF[10: 171 Product specification SAA7108E; SAA7109E D[7:4] D[3:0] (41H TO 57H) (41H TO 57H) DT[3:0] 62H[3:0] DT[3:0] 62H[3:0] (FIELD 1) (FIELD 2) 0000 0000 0001 0001 0010 0010 0011 ...

Page 172

... ANC header framing; see Fig.38 and Table 50 11 1110 DID[5:0] = 3EH SAV/EAV framing, with FVREF = 1 11 1111 DID[5:0] = 3FH SAV/EAV framing, with FVREF = 0 SYMBOL VALUE SDID[5:0] 00H default 172 Product specification SAA7108E; SAA7109E CONTROL BITS 5AH[7:0] VOFF[7:0] 00H 38H 03H 06H FUNCTION FUNCTION ...

Page 173

... Closed Caption in the last frame 1 Closed Caption detected SYMBOL F21_N field ID as seen by the VBI slicer; for field LN[8:4] line number LN[3:0] DT[3:0] data type; according to Table 44 173 Product specification SAA7108E; SAA7109E FUNCTION DESCRIPTION CONTROL BITS SMOD TEB TEA ...

Page 174

... X port output is enabled by pin XTRI at logic 0 X port output is enabled by pin XTRI at logic 1 XRDY output signal is A/B task flag from event handler ( XRDY output signal is ready signal from scaler path (XRDY = 1 means SAA7108E; SAA7109E is ready to receive data) Note don’t care 2001 Dec 12 SAA7108E ...

Page 175

... IGPV is a V-gate signal, framing scaled output lines IGPV is the V-reference signal from scaler input IGPV is a vertical trigger pulse, derived from V-gate IGPV is a vertical trigger pulse derived from input V-reference Note don’t care. 2001 Dec 12 SAA7108E; SAA7109E CONTROL BITS IDV1 ...

Page 176

... IGPH at default polarity (1 = active) IGPH is inverted IGPV at default polarity (1 = active) IGPV is inverted IGP1 at default polarity IGP1 is inverted IGP0 at default polarity IGP0 is inverted Note don’t care. 2001 Dec IG0P 176 Product specification SAA7108E; SAA7109E CONTROL BITS ISWP1 ISWP0 CONTROL BITS IG1P IRVP IRHP ...

Page 177

... I PORT FIFO FLAG CONTROL AND ARBITRATION FAE FIFO flag almost empty level <16 Dwords <8 Dwords <4 Dwords 0 Dwords FAF FIFO flag almost full level 16 Dwords 24 Dwords 28 Dwords 32 Dwords Note don’t care. 2001 Dec 12 SAA7108E; SAA7109E CONTROL BITS VITX1 VITX0 ...

Page 178

... I port output is enabled by software I port output is enabled by pin ITRI at logic 0 I port output is enabled by pin ITRI at logic 1 2001 Dec 12 recommended for ICKS1 = 1 1 clock cycle recommended 2 1 clock cycle + approximately 2 178 Product specification SAA7108E; SAA7109E CONTROL BITS (2) (2) IPCK3 IPCK2 IPCK1 ...

Page 179

... ICLK source is the X port (refer to subaddresses 80H and 91H/C1H) Scaler is in operational mode Scaler is in Power-down mode; scaler in Power-down stops I port output Audio clock generation active Audio clock generation in Power-down and output disabled Note don’t care. 2001 Dec 12 SAA7108E; SAA7109E CONTROL BITS CH4EN CH2EN ...

Page 180

... Dec 12 SAA7108E; SAA7109E (1) FUNCTION 2 C-bus read. CONTROL BITS D7 AND D6 ...

Page 181

... SELECTION Only if XRQT[83H[2 scaler input source reacts on SAA7108E; SAA7109E request Scaler input source is a continuous data stream, which cannot be interrupted (must be logic 1 if SAA7108E; SAA7109E decoder part is source of scaler or XRQT[83H[2 Scaler input source is data from decoder, data type is provided according to Table 44 ...

Page 182

... X port field ID is state of XRH at reference edge on XRV (defined by XFDV) Field ID (decoder and X port field ID) is inverted Reference edge for field detection is falling edge of XRV Reference edge for field detection is rising edge of XRV Note don’t care. 2001 Dec 12 SAA7108E; SAA7109E CONTROL BITS (2) FSC2 ...

Page 183

... Dwords are transferred 16-bit word wise via IPD and HPD, see subaddress 85H bits ISWP1 and ISWP0 No ITU 656 like SAV/EAV codes are available ITU 656 like SAV/EAV codes are inserted in the output data stream, framed by a qualifier Note don’t care. 2001 Dec 12 SAA7108E; SAA7109E CONTROL BITS XCODE XDH ...

Page 184

... Dec 12 -C output, in between output, in between line is output line is output line is output line is output [95H[3:0]] B [C5H[3:0]] (1) XO11 XO10 XO9 XO8 XO7 XO6 XO5 XO4 XO3 XO2 XO1 XO0 184 Product specification SAA7108E; SAA7109E CONTROL BITS FOI1 FOI0 FSI2 CONTROL BITS A [94H[7:0]] ...

Page 185

... YO11 YO10 YO9 YO8 YO7 YO6 YO5 YO4 YO3 YO2 YO1 YO0 CONTROL BITS A [9BH[3:0]] B [CBH[3:0]] YS11 YS10 YS9 YS8 YS7 YS6 YS5 YS4 YS3 YS2 YS1 YS0 185 Product specification SAA7108E; SAA7109E A [96H[7:0]] B [C6H[7:0 [98H[7:0]] B [C8H[7:0 2), will result in field 2), will result in field dropping. ...

Page 186

... XD11 XD10 XD9 XD8 XD7 XD6 XD5 XD4 XD3 XD2 XD1 XD0 [9FH[3:0]] B [CFH[3:0]] YD11 YD10 YD9 YD8 YD7 YD6 YD5 YD4 YD3 YD2 YD1 YD0 XPSC5 XPSC4 XPSC3 XPSC2 XPSC1 XPSC0 186 Product specification SAA7108E; SAA7109E CONTROL BITS A [9CH[7:0]] B [CCH[7:0 CONTROL BITS A [9EH[7:0]] B [CEH[7:0 ...

Page 187

... Prescaler output is renormalized by gain factor = Prescaler output is renormalized by gain factor = Weighting of all accumulated samples is factor 1; e.g. XACL = 4 sequence Weighting of samples inside sequence is factor 2; e.g. XACL = 4 sequence Note don’t care. 2001 Dec 12 SAA7108E; SAA7109E CONTROL BITS XACL5 XACL4 XACL3 XACL2 XACL1 XACL0 ... ... 1 1 ...

Page 188

... CONTROL BITS CONT7 CONT6 CONT5 CONTROL BITS SATN7 SATN6 SATN5 [A9H[7:4]] A [A9H[3:0]] B [D9H[7:4]] B [D9H[3:0]] (1) XSCY[15:12] XSCY[11:8] 0000 0000 0000 0000 0000 0001 188 SAA7108E; SAA7109E BRIG4 BRIG3 BRIG2 CONT4 CONT3 CONT2 SATN4 SATN3 SATN2 CONTROL BITS A [A8H[7:4]] B [D8H[7:4]] XSCY[7:4] 0000 ...

Page 189

... XPHC7 XPHC6 XPHC5 XPHC4 XPHC3 XPHC2 XPHC1 XPHC0 CONTROL BITS A [B1H[7:4]] A [B1H[3:0]] B [E1H[7:4]] B [E1H[3:0]] YSCY[15:12] YSCY[11:8] 0000 0000 0000 0011 0000 0100 0000 0100 1111 1111 189 Product specification SAA7108E; SAA7109E [ACH[7:4]] A [ACH[3:0]] B [DCH[7:4]] B [DCH[3:0]] XSCC[7:4] XSCC[3:0] 0000 0000 1111 ...

Page 190

... CONTROL BITS YPC07 YPC06 YPC05 YPC04 CONTROL BITS YPY07 YPY06 YPY05 YPY04 190 Product specification SAA7108E; SAA7109E A [B2H[7:4]] A [B2H[3:0]] B [E2H[7:4]] B [E2H[3:0]] YSCC[7:4] YSCC[3:0] 0000 0001 1111 1111 CONTROL BITS D4 AND D0 YMIR YMODE YPC03 YPC02 YPC01 YPC00 YPY03 ...

Page 191

... PROGRAMMING START SET-UP OF DIGITAL VIDEO DECODER PART 19.1 Decoder part The given values force the following behaviour of the SAA7108E; SAA7109E decoder part: The analog input AI11 expects an NTSC M, PAL and I or SECAM signal in CVBS format; analog anti-alias filter and AGC active ...

Page 192

... CM99, UPTCV, AOSL1, AOSL0, XTOUTE, OLDSB, APCK1 and APCK0 VSTO7 to VSTO0 LLCE, LLC2E VGPS, VSTO8 and VSTA8 RAWG7 to RAWG0 RAWO7 to RAWO0 INTL, HLVLN, FIDT, GLIMT, GLIMB, WIPA, COPRO and RDCAP 192 Product specification SAA7108E; SAA7109E VALUES (HEX) PAL B, D, NTSC M SECAM G, H AND ...

Page 193

... Philips Semiconductors PC-CODEC 19.2 Audio clock generation part The given values force the following behaviour of the SAA7108E; SAA7109E audio clock generation part: Used crystal is 24.576 MHz Expected field frequency is 59.94 Hz (e.g. NTSC M standard) Generated audio master clock frequency at pin AMCLK is 256 ...

Page 194

... PC-CODEC 19.3 Data slicer and data type control part The given values force the following behaviour of the SAA7108E; SAA7109E VBI data slicer part: Closed captioning data is expected at line 21 of field 1 (60 Hz/525 line system) All other lines are processed as active video ...

Page 195

... The maximum horizontal zoom is limited to approximately 3.5, due to internal data path restrictions input (if no 16-bit B R 195 Product specification SAA7108E; SAA7109E INPUT OUTPUT SCALE WINDOW WINDOW RATIOS 720 240 720 240 prsc = 1; ...

Page 196

... Prefiltering and prescaling A0 integer prescale (value ‘00’ not allowed) A1 accumulation length for prescaler A2 FIR prefilter and prescaler DC normalization A4 scaler brightness control A5 scaler contrast control A6 scaler saturation control 2001 Dec 12 SAA7108E; SAA7109E EXAMPLE 1 EXAMPLE 2 EXAMPLE 3 EXAMPLE 4 HEX DEC HEX DEC ...

Page 197

... B1 B2 vertical scaling increment for chrominance B3 B4 vertical scaling mode control vertical phase offsets luminance and chrominance (needs to be used for interlace correct scaled output) 2001 Dec 12 SAA7108E; SAA7109E EXAMPLE 1 EXAMPLE 2 EXAMPLE 3 EXAMPLE 4 HEX DEC HEX DEC 00 1024 AA 938 04 03 ...

Page 198

... OUTLINE VERSION IEC SOT472-1 2001 Dec scale 15.2 13.7 15.2 13.7 1.0 13.0 14.8 13.0 14.8 13.0 REFERENCES JEDEC EIAJ 198 SAA7108E; SAA7109E detail 1.65 0.15 0.35 0.3 0.1 1.10 EUROPEAN PROJECTION Product specification SOT472-1 ISSUE DATE 99-12-02 00-03-04 ...

Page 199

... If wave soldering is used the following conditions must be observed for optimal results: 2001 Dec 12 SAA7108E; SAA7109E Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave. For packages with leads on two sides and a pitch (e): – ...

Page 200

... This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. 200 Product specification SAA7108E; SAA7109E SOLDERING METHOD WAVE REFLOW suitable (2) suitable ...