CS4328-KS Cirrus Logic, Inc., CS4328-KS Datasheet

CS4328-KS

Available stocks

Related parts for CS4328-KS

CS4328-KS Summary of contents

Page 1

... The CS4328 also includes an extremely flexible serial port utilizing two select pins to support four different interface modes. The master clock can be either 256 or 384 times the input word rate, supporting various audio environ- ments. ORDERING INFORMATION: CS4328-KP CS4328-KS CS4328-BP CS4328-BS CDB4328 VD+ DGND AGND1 16 ...

Page 2

... VOUT 3.8 4.0 IA IA- - -40 ID 650 PSRR - 50 Specifications are subject to change without notice. CS4328 = -40 to +85 C for B grade; VA+,VD+ A CS4328-B Max Min Typ Max +70 -40 + 120 - -90 - -88 -85 -73 - -75 -70 -33 - -35 -30 0 0 23 21.6 +0.2 -0.05 +0.1 +0 ...

Page 3

... Symbol Min V IH 70%VD 4 (Note (AGND1-3, DGND = 0V, all voltages with respect to ground.) Symbol Min VD+ -0.3 VA+ -0.3 VA- 0 IND -0 -55 T stg -65 Symbol Min VD+ 4.75 VA+ 4.75 VA- -4.75 - CS4328 Typ Max Units - - V - 30%VD 0 1.0 A Max Units 6.0 V 6 (VD+)+0.4 V 125 C 150 ...

Page 4

... Serial Input Timing (Modes 0, 1, &3) 4 5%; VA- = -5V 5%; Inputs: Logic 0 = 0V, Logic 1 = VD+, C Symbol XTI/XTO XTI/XTO t bickl t bickh t bickw (Note 6) t blrd (Note 6) t blrs (Note 6) t sbs (Note 6) t bsh LRCK t bickh t bickl BICK t bsh SDATAI CS4328 = 20 pF) L Min Typ Max 10.7 - 19.2 - 7.1 - 13.9 0.384 - 19.2 - 0.256 - 13 ...

Page 5

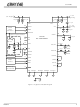

... DS62F3 16 VD+ LRCK BICK SDATAI 7 CS4328 NC D/A CONVERTER NC XTO XTI ACKO ACKI CKS DIF0 DIF1 9 RST TST DGND AGND3 AGND2 Figure 1. Typical Connection Diagram CS4328 + 0 VA+ 5 VA- 0 VREF- 0 AOUTL 10 nF NPO 51 26 AOUTR 10 nF NPO 6 CMPO 8 CMPI 21 CALO ...

Page 6

... XTI/XTO or power will require a "kick-start" pulse to resume operation. Serial Data Interface Data is input to the CS4328 via three serial input pins; SDATAI is the serial data input, BICK is the serial data clock and LRCK defines the chan- nel and delineation of data. The DAC supports four serial data formats which are selected via the digital input format pins DIF0 and DIF1 ...

Page 7

... DAC. Bringing RST high will Figure begin a calibration cycle and initialize these reg- 3 isters Muting 5 There are two types of mutes that can be imple- mented with the CS4328. The first is a -50 dB CS4328 Exit Reset 7 ...

Page 8

... CS4328 Right Channel ...

Page 9

... The rms noise present at the output will typically below fullscale. Following a total of 4096 LRCK cycles with 0 input data the output of the CS4328 will mute and lower the output rms noise to a minimum of 120 dB below fullscale. Upon release of the MUTE command and non-zero input data the CS4328 output mute will immediately release ...

Page 10

... Figure 17 shows the monotonicity test result plot. The input data to the CS4328 is +1 LSB, -1 LSB four times, then +2 LSB, -2 LSB four times and so on, until +10 LSB, -10 LSB. This data pattern is taken from track 21 of the CD-1 test disk ...

Page 11

... FREQ(kHz) CRYSTAL 2.000 1.583 1.167 0.750 0.333 -0.083 -0.500 68.6 78.4 88.2 98.0 0.0 95.8 CS4328 THD+N(dBr) vs GENAMP(dBFS) -80 -70 -60 -50 -40 -30 -20 BANDPASS(dBr) vs -110 -100 -90 -80 Figure 13. Fade-to-Noise Linearity IMPULSE AMP1(V) vs 192 287 383 479 575 670 Figure 14. Impulse Response -10 0 LEVEL(dBr) ...

Page 12

... Figure 17. Monotonicity Test (16-bit data) vs TIME(msec) CRYSTAL 1k 0dBFFT 0 -20 -40 -60 -80 -100 -120 -140 2.00 2.50 3.00 20 1KM10DB AMP1(dBr) 20 100 1k Figure 19. 1 kHz, -10 dB Input FFT Plot CS4328 MONOTON AMP1(uV AMP1(dBr) 100 1k Figure 18. 1 kHz Input FFT Plot vs FREQ(Hz) 10k 20k TIME(msec) 40 ...

Page 13

... The CS4328 architecture can be considered in five blocks: Interpolation, sample/hold, delta- sigma modulation, D/A conversion, and analog filtering. Audio data is input to the CS4328 digital inter- polation filter which removes images of the input signal that are present at multiples of the input sample frequency, Fs (Figure 21). Following the ...

Page 14

... The final stage of the CS4328 is made 5th order switched-capacitor low pass filter and a 2nd order continuous time filter. The switched- capacitor filter eliminates out-of-band energy re- su lting from the n oise shaping process (Figure 25) ...

Page 15

... Input Frequency (kHz) Figure 29. Combined Digital and Analog Filter Frequency Response 0 -10 -20 -30 -40 -50 -60 -70 -80 -90 -100 -110 Input Frequency (kHz) Figure 30. Combined Digital and Analog Filter Transition Band DS62F3 CS4328 15 ...

Page 16

... TST BICK 10 19 CKS SDATAI SERIAL DATA INPUT 11 18 DIF1 DGND DIGITAL GROUND 12 17 DIF0 VD XTI XTO 14 15 CS4328 CALIBRATION INPUT ANALOG CLOCK INPUT NO CONNECT CALIBRATION OUTPUT LEFT/RIGHT CLOCK INPUT SERIAL BIT CLOCK INPUT DIGITAL POWER CRYSTAL OSCILLATOR OUTPUT DS62F3 ...

Page 17

... Two’s complement MSB-first serial data of either bits is input on this pin. The data is clocked into the CS4328 via the BICK clock and the channel is determined by the LRCK clock. The format for the previous two clocks is determined by the Digital Input Format pins, DIF0 ...

Page 18

... Connection, PINS 7, 23. These two pins are bonded out to test outputs. They must not be connected to any external component or any length of PC trace. TST -Test Input, PIN 10. Allows access to the CS4328 test modes, which are reserved for factory use. Must be tied to DGND. 18 CS4328 ...

Page 19

... Gain Error - The deviation from the nominal full scale analog output for a full scale digital input. Gain Drift - The change in gain value with temperature. Units in ppm/ C. Offset Error - The deviation of the mid-scale transition (111...111 to 000...000) from the ideal (AGND). Units in mV. DS62F3 CS4328 19 ...

Page 20

D SEATING PLANE e1 B1 NOTES: 1. POSITIONAL TOLERANCE OF LEADS SHALL BE WITHIN 0.25mm (0.010") AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER. 2. DIMENSION eA TO CENTER OF LEADS WHEN ...

Page 21

... Fax: (512) 445 7581 http://www.crystal.com General Description The CDB4328 evaluation board allows fast evaluation of the CS4328 18-bit, stereo D/A converter. The board provides an analog output interface via BNC connec- tors for both channels. Evaluation requires an analog signal analyzer, a digital signal source, and a power supply ...

Page 22

... Serial Data Interface Figure 1 shows that there are two options for in- puting serial data into the CS4328. Serial data can be provided via the SDATA BNC connector on the evaluation board. BNC connectors for SCLK, the serial data input clock, and L/R, the clock that defines the channel and delineates the data, are also provided on the evaluation board ...

Page 23

... CLK is selected, the master clock is provided by one of two sources. The 12.288 MHz clock sig- nal provided by U8 can be used as the master clock for both the CS4328 and the external sys- tem that provides the serial data to the board. The other option is for a master clock that is ...

Page 24

... When 8412 is selected by JP3, the master clock for the CS4328 is provided by the MCK output of the CS8412. The CKS pin of the CS4328 can be pulled either high or low via JP2. This determines whether the master clock frequency has to be 384X or 256X the input word rate ...

Page 25

DS62DB2 CDB4328 25 ...

Page 26

... DIF0 low). Modify the jumpers located near pins 12 and 13 of the CS4328. JP2 sets the clock to sample frequency ratio (CKS) on the CS4328 and is set low for a 256 ratio. JP3 selects the source of SDATA, SCLK and L/R that will be provided to the converter and should ...

Page 27

Figure 4. Top Ground Plane Layer (NOT TO SCALE) 28 CDB4328 DS62DB2 ...

Page 28

Figure 5. Bottom Trace Layer (NOT TO SCALE) DS62DB2 CDB4328 29 ...

Page 29

Figure 5. Silk Screen Layer (NOT TO SCALE) CDB4328 DS62DB2 ...

Page 30

Notes • ...

Page 31

TM Smart Analog is a Trademark of Crystal Semiconductor Corporation ...