AM29DL320GB120WDI Meet Spansion Inc., AM29DL320GB120WDI Datasheet

AM29DL320GB120WDI

Related parts for AM29DL320GB120WDI

AM29DL320GB120WDI Summary of contents

Page 1

Am29DL320G Data Sheet Continuity of Specifications Continuity of Ordering Part Numbers For More Information Publication Number 25769 Revision C Amendment 2 Issue Date September 24, 2004 ...

Page 2

THIS PAGE LEFT INTENTIONALLY BLANK. ...

Page 3

For new designs involving TSOP packages, S29JL032H supersedes Am29DL320G and is the factory-recom- mended migration path. Please refer to the S29JL032H Datasheet for specifications and ordering information. For new designs involving Fine-pitch BGA (FBGA) packages, S29PL032J supersedes Am29DL320G and is ...

Page 4

GENERAL DESCRIPTION The Am29DL320G megabit, 3.0 volt-only flash memory device, organized as 2,097,152 words of 16 bits each or 4,194,304 bytes of 8 bits each. Word mode data appears on DQ15–DQ0; byte mode data appears on DQ7–DQ0. ...

Page 5

TABLE OF CONTENTS Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 5 Block Diagram . . . . . . . . . . ...

Page 6

PRODUCT SELECTOR GUIDE Part Number Speed Rating Standard Voltage Range: V Max Access Time (ns) CE# Access (ns) OE# Access (ns) BLOCK DIAGRAM Mux A20–A0 RY/BY# A20–A0 STATE RESET# CONTROL WE# & COMMAND CE# REGISTER BYTE# ...

Page 7

CONNECTION DIAGRAMS A15 1 A14 2 A13 3 A12 4 A11 5 A10 A19 9 A20 10 WE RESET WP#/ACC 14 RY/BY A18 A17 ...

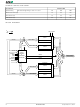

Page 8

CONNECTION DIAGRAMS C7 A13 WE# RESET# C4 RY/BY# WP#/ACC Special Package Handling Instructions Special handling is required for Flash Memory products in molded packages (TSOP, BGA, SSOP, PLCC, PDIP). The package and/or data ...

Page 9

PIN DESCRIPTION A20– Addresses DQ14–DQ0 = 15 Data Inputs/Outputs DQ15/A-1 = DQ15 (Data Input/Output, word mode), A-1 (LSB Address Input, byte mode) CE# = Chip Enable OE# = Output Enable WE# = Write Enable WP#/ACC = Hardware Write ...

Page 10

ORDERING INFORMATION Standard Products AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the following: Am29DL320G DEVICE NUMBER/DESCRIPTION Am29DL320G 32 Megabit ( ...

Page 11

DEVICE BUS OPERATIONS This section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register itself does not occupy any addressable memory loca- tion. The register is a latch ...

Page 12

Each bank remains enabled for read access until the command register contents are altered. See “Requirements for Reading Array Data” for more information. Refer to the ...

Page 13

While in sleep mode, output data is latched and always available to the system the DC Characteristics table represents the CC5 automatic sleep mode current specification. RESET#: ...

Page 14

Sector Address Sector A20–A12 SA0 000000xxx SA1 000001xxx SA2 000010xxx SA3 000011xxx SA4 000100xxx SA5 000101xxx SA6 000110xxx SA7 000111xxx SA8 001000xxx SA9 001001xxx SA10 001010xxx SA11 001011xxx SA12 001100xxx SA13 001101xxx SA14 001110xxx SA15 001111xxx SA16 010000xxx SA17 010001xxx ...

Page 15

Table 2. Top Boot Sector Addresses (Continued) Sector Address Sector A20–A12 SA48 110000xxx SA49 110001xxx SA50 110010xxx SA51 110011xxx SA52 110100xxx SA53 110101xxx SA54 110110xxx SA55 110111xxx SA56 111000xxx SA57 111001xxx SA58 111010xxx SA59 111011xxx SA60 111100xxx SA61 111101xxx SA62 ...

Page 16

Sector Address Sector A20–A12 SA0 000000000 SA1 000000001 SA2 000000010 SA3 000000011 SA4 000000100 SA5 000000101 SA6 000000110 SA7 000000111 SA8 000001xxx SA9 000010xxx SA10 000011xxx SA11 000100xxx SA12 000101xxx SA13 000110xxx SA14 000111xxx SA15 001000xxx SA16 001001xxx SA17 001010xxx ...

Page 17

Table 4. Bottom Boot Sector Addresses (Continued) Sector Address Sector A20–A12 SA48 101001xxx SA49 101010xxx SA50 101011xxx SA51 101100xxx SA52 101101xxx SA53 101110xxx SA54 101111xxx SA55 111000xxx SA56 110001xxx SA57 110010xxx SA58 110011xxx SA59 110100xxx SA60 110101xxx SA61 110110xxx SA62 ...

Page 18

Autoselect Mode The autoselect mode provides manufacturer and de- vice identification, and sector protection verification, through identifier codes output on DQ7–DQ0. This mode is primarily intended for programming equip- ment to automatically match a device to be pro- grammed with ...

Page 19

Sector/Sector Block Protection and Unprotection (Note: For the following discussion, the term “sector” applies to both sectors and sector blocks. A sector block consists of two or more adjacent sectors that are protected or unprotected at the same time (see ...

Page 20

The alternate method intended only for programming equipment requires V on address pin A9 and OE#. ID This method is compatible with programmer routines written for earlier 3.0 volt-only AMD flash devices. Publication number 22244 contains further details; contact an ...

Page 21

START PLSCNT = 1 RESET Wait 1 µs No First Write Temporary Sector Cycle = 60h? Unprotect Mode Yes Set up sector address Sector Protect: Write 60h to sector address with ...

Page 22

TM SecSi (Secured Silicon) Sector Flash Memory Region The SecSi (Secured Silicon) Sector feature provides a 256-byte Flash memory region that enables perma- nent part identification through an Electronic Serial Number (ESN). The SecSi Sector uses a SecSi Sector Indicator ...

Page 23

START If data = 00h, RESET# = SecSi Sector unprotected. If data = 01h, SecSi Sector is Wait 1 µs protected. Write 60h to any address Remove V from RESET# Write 40h to SecSi ...

Page 24

Addresses Addresses (Word Mode) (Byte Mode) 10h 20h 11h 22h 12h 24h 13h 26h 14h 28h 15h 2Ah 16h 2Ch 17h 2Eh 18h 30h 19h 32h 1Ah 34h Addresses Addresses (Word Mode) (Byte Mode) 1Bh 36h 1Ch 38h 1Dh 3Ah ...

Page 25

Addresses Addresses (Word Mode) (Byte Mode) 27h 4Eh 28h 50h 29h 52h 2Ah 54h 2Bh 56h 2Ch 58h 2Dh 5Ah 2Eh 5Ch 2Fh 5Eh 30h 60h 31h 62h 32h 64h 33h 66h 34h 68h 35h 6Ah 36h 6Ch 37h 6Eh ...

Page 26

Addresses Addresses (Word Mode) (Byte Mode) 4Ch 98h 4Dh 9Ah 4Eh 9Ch 4Fh 9Eh COMMAND DEFINITIONS Writing specific address and data commands or se- quences into the command register initiates device op- erations. Table 13 defines the valid register command ...

Page 27

The autoselect command may not be written while the device is actively programming or erasing in the other bank. The ...

Page 28

V on the WP#/ACC pin, the device automatically en- HH ters the Unlock Bypass mode. The system may then write the two-cycle Unlock Bypass program command sequence. The device uses the higher voltage on the WP#/ACC pin to accelerate the ...

Page 29

The system must rewrite the com- mand sequence and any additional addresses and commands. The system can monitor DQ3 to determine if the sec- tor erase timer has ...

Page 30

Command Sequence (Note 1) Addr Read (Note 6) 1 Reset (Note 7) 1 Word Manufacturer ID 4 Byte Word Device ID (Note 9) 4 Byte Word SecSi™ Sector Factory 4 Protect (Note 10) Byte Sector/Sector Block Word Protect Verify 4 ...

Page 31

WRITE OPERATION STATUS The device provides several bits to determine the status of a program or erase operation: DQ2, DQ3, DQ5, DQ6, and DQ7. Table 14 and the following subsections describe the function of these bits. DQ7 and DQ6 each ...

Page 32

RY/BY#: Ready/Busy# The RY/BY dedicated, open-drain output pin which indicates whether an Embedded Algorithm is in progress or complete. The RY/BY# status is valid after the rising edge of the final WE# pulse in the command sequence. Since ...

Page 33

DQ2: Toggle Bit II The “Toggle Bit II” on DQ2, when used with DQ6, indi- cates whether a particular sector is actively erasing (that is, the Embedded Erase algorithm is in progress), or whether that sector is erase-suspended. Toggle Bit ...

Page 34

Status Embedded Program Algorithm Standard Mode Embedded Erase Algorithm Erase Suspended Sector Erase-Suspend- Erase Read Suspend Non-Erase Mode Suspended Sector Erase-Suspend-Program Notes: 1. DQ5 switches to ‘1’ when an Embedded Program or Embedded Erase operation has exceeded the maximum timing ...

Page 35

ABSOLUTE MAXIMUM RATINGS Storage Temperature Plastic Packages . . . . . . . . . . . . . . . –65°C to +150°C Ambient Temperature with Power Applied . . . . . . . . . . ...

Page 36

DC CHARACTERISTICS CMOS Compatible Parameter Symbol Parameter Description I Input Load Current Input Load Current LIT I Output Leakage Current LO I Reset# Input Load Current LR V Active Read Current CC I CC1 (Notes 1, 2) ...

Page 37

DC CHARACTERISTICS Zero-Power Flash 500 1000 Note: Addresses are switching at 1 MHz Figure 10. I Current vs. Time (Showing Active and Automatic Sleep Currents) CC1 ...

Page 38

TEST CONDITIONS Device Under Test C 6.2 kΩ L Note: Diodes are IN3064 or equivalent Figure 12. Test Setup KEY TO SWITCHING WAVEFORMS WAVEFORM Don’t Care, Any Change Permitted 3.0 V Input 1.5 V 0.0 V Figure 13. Input Waveforms ...

Page 39

AC CHARACTERISTICS Read-Only Operations Parameter JEDEC Std. Description t t Read Cycle Time (Note 1) AVAV Address to Output Delay AVQV ACC t t Chip Enable to Output Delay ELQV Output Enable to Output ...

Page 40

AC CHARACTERISTICS Hardware Reset (RESET#) Parameter JEDEC Std RESET# Pin Low (During Embedded Algorithms) t Ready to Read Mode (See Note) RESET# Pin Low (NOT During Embedded t Ready Algorithms) to Read Mode (See Note) t RESET# Pulse Width RP ...

Page 41

AC CHARACTERISTICS Word/Byte Configuration (BYTE#) Parameter JEDEC Std Description t /t CE# to BYTE# Switching Low or High ELFL ELFH t BYTE# Switching Low to Output HIGH Z FLQZ t BYTE# Switching High to Output Active FHQV CE# OE# BYTE# ...

Page 42

AC CHARACTERISTICS Erase and Program Operations Parameter JEDEC Std Description t t Write Cycle Time (Note 1) AVAV Address Setup Time AVWL AS t Address Setup Time to OE# low during toggle bit polling ASO t t ...

Page 43

AC CHARACTERISTICS Program Command Sequence (last two cycles Addresses 555h CE# OE# WE Data RY/BY VCS Notes program address program data Illustration shows device in word ...

Page 44

AC CHARACTERISTICS Erase Command Sequence (last two cycles Addresses 2AAh CE Data 55h RY/BY# t VCS V CC Notes sector address (for Sector Erase Valid ...

Page 45

AC CHARACTERISTICS t WC Valid PA Addresses t AH CE# OE WE# t WPH Valid Data In WE# Controlled Write Cycle Figure 21. Back-to-back Read/Write Cycle Timings t RC Addresses VA t ACC t ...

Page 46

AC CHARACTERISTICS Addresses CE# t OEH WE# OE Valid Data DQ6/DQ2 RY/BY# Note Valid address; not required for DQ6. Illustration shows first two status cycle after command sequence, last status read cycle, and array data read ...

Page 47

AC CHARACTERISTICS Temporary Sector Unprotect Parameter JEDEC Std Description t V Rise and Fall Time (See Note) VIDR Rise and Fall Time (See Note) VHH HH RESET# Setup Time for Temporary Sector t RSP Unprotect RESET# Hold ...

Page 48

AC CHARACTERISTICS RESET# SA, A6, A1, A0 Sector/Sector Block Protect or Unprotect Data 60h 1 µs CE# WE# OE# * For sector protect For sector unprotect, A6 ...

Page 49

AC CHARACTERISTICS Alternate CE# Controlled Erase and Program Operations Parameter JEDEC Std Description t t Write Cycle Time (Note 1) AVAV Address Setup Time AVWL Address Hold Time ELAX Data Setup ...

Page 50

AC CHARACTERISTICS 555 for program 2AA for erase Addresses WE# OE# CE Data t RH RESET# RY/BY# Notes: 1. Figure indicates last two bus cycles of a program or erase operation ...

Page 51

ERASE AND PROGRAMMING PERFORMANCE Parameter Sector Erase Time Chip Erase Time Byte Program Time Accelerated Byte/Word Program Time Word Program Time Byte Mode Chip Program Time (Note 3) Word Mode Notes: 1. Typical program and erase times assume the following ...

Page 52

PHYSICAL DIMENSIONS FBD063—63-ball Fine-Pitch Ball Grid Array (FBGA Am29DL320G Dwg rev AF; 10/99 September 27, 2004 ...

Page 53

PHYSICAL DIMENSIONS FBD048—Fine-Pitch Ball Grid Array FBD 048 6. 12.00 mm PACKAGE 1.20 0.20 0.94 0.84 12.00 BSC 6.00 BSC 5.60 BSC 4.00 BSC 0.25 0.30 0.35 0.80 BSC 0.40 BSC ...

Page 54

PHYSICAL DIMENSIONS TS 048—Thin Small Outline Package 52 Am29DL320G Dwg rev AA; 10/99 September 27, 2004 ...

Page 55

PHYSICAL DIMENSIONS LAA064—64-ball Fortified Ball Grid Array ( package September 27, 2004 F BGA) Am29DL320G 53 ...

Page 56

REVISION SUMMARY Revision A (December 6, 2001) Initial release. Revision A+1 (February 19, 2002) Ordering Information Corrected package marking for FBGA package. Revision B (July 31, 2002) Global Added LAA064 package. Ordering Information Corrected package marking ...

Page 57

Colophon The products described in this document are designed, developed and manufactured as contemplated for general use, including without limita- tion, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as ...

Page 58

Sales Offices and Representatives North America ALABAMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...