LMH0031VS/NOPB National Semiconductor, LMH0031VS/NOPB Datasheet - Page 30

LMH0031VS/NOPB

Manufacturer Part Number

LMH0031VS/NOPB

Description

IC DESER/DESCRAM DGTL VID 64TQFP

Manufacturer

National Semiconductor

Type

Descrambler/Deserializerr

Datasheet

1.LMH0031VSNOPB.pdf

(31 pages)

Specifications of LMH0031VS/NOPB

Applications

SDTV/HDTV

Mounting Type

Surface Mount

Package / Case

64-TQFP, 64-VQFP

Input Voltage

3.3 V

Supply Voltage (max)

3.45 V

Supply Voltage (min)

3.15 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

For Use With

SD131EVK - BOARD EVALUATION LMH0031

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LMH0031VS/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

www.national.com

Application Information

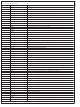

The control voltage output from R

the loop filter consisting of a 22.1kΩ resistor in series with a

10nF capacitor, combined in parallel with a 100pF capacitor.

This gives a loop bandwidth of 1.5kHz. Since the control

voltage is limited to around 2.1V, it requires a level shifter to

get the entire pull range on the VCXO. National’s LMC7101

is recommended with 100kΩ and 182kΩ resistors as shown

in Figure 7 to provide a gain of 1.55, sufficient to drive a 3.3V

VCXO.

Recommended VCXOs from SaRonix (141 Jefferson Drive,

Menlo Park, CA 94025, USA) include the ST1308AAB-74.25

for high definition and the ST1307BAB-27.00 for standard

definition. Dual VCXOs require some supporting logic to

select the appropriate VCXO. This requires the use of For-

mat[4] (SD/HD) and Lock Detect, which are mapped at

power-on to I/O Port Bit 3 and I/O Port Bit 4, respectively.

BB

is externally filtered by

FIGURE 7. Using Dual VCXOs for VCLK Example

(Continued)

30

These two signals pass through an AND gate (Fairchild

Semiconductor’s NC7SZ08 or similar). Its output is high

when both Lock Detect and Format[4] are high, which indi-

cates a valid high-definition signal is present. The VCXOs

are buffered to control the transition times and to allow easy

selection. The output of the AND gate is used to control the

Output Enable (OE) function of the buffers. The 74.25MHz

VCXO is buffered with the NC7SZ126 with the AND gate

output connected to the OE pin of the NC7SZ126, and the

27.00MHz VCXO is buffered with the NC7SZ125 with the

AND gate output connected to the OE pin of the NC7SZ125.

This circuit uses the 27.00MHz VCXO as default and en-

ables the 74.25MHz VCXO when a valid high-definition sig-

nal is present. The outputs from the buffers are daisy-

chained together and sent to the LMH0031’s V

to other devices, such as the LMH0030 serializer.

20179614

CLK

in addition