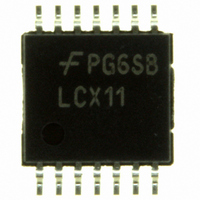

74LCX11MTCX Fairchild Semiconductor, 74LCX11MTCX Datasheet

74LCX11MTCX

Specifications of 74LCX11MTCX

Available stocks

Related parts for 74LCX11MTCX

74LCX11MTCX Summary of contents

Page 1

... DQFN package available in Tape and Reel only. Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number. All packages are lead free per JEDEC: J-STD-020B standard. ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 General Description The LCX11 is a triple 3-input AND gate with buffered outputs ...

Page 2

... Connection Diagrams Pin Assignments for SOIC, SOP, and TSSOP (Top View) Pad Assignments for DQFN (Top Through View) Pin Description Pin Names Description Inputs Outputs n ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 Logic Symbol IEEE/IEC Logic Diagram 2 www.fairchildsemi.com ...

Page 3

... CC V 2.7V–3. 2.3V–2. Free-Air Operating Temperature Input Edge Rate, V Note: 3. Unused inputs must be held HIGH or LOW. They may not float. ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 Parameter (2) GND I (3) Parameter 0.8V–2.0V Rating –0.5V to +7.0V –0.5V to +7.0V – ...

Page 4

... Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW ( LOW-to-HIGH (t OSHL ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 V (V) Conditions CC 2.3– ...

Page 5

... Dynamic Switching Characteristics Symbol Parameter V Quiet Output Dynamic Peak V OLP V Quiet Output Dynamic Valley V OLV Capacitance Symbol Parameter C Input Capacitance IN C Output Capacitance OUT C Power Dissipation Capacitance PD ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 V (V) Conditions CC 3.3 C 50pF, V 3.3V 2.5 C 30pF, V 2.5V 3.3 C 50pF ...

Page 6

... Waveform for Inverting and Non-Inverting Functions Propagation Delay. Pulse Width and t 3-STATE Output Low Enable and Disable Times for Logic Figure 2. Waveforms (Input Characteristics 1MHz, t ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 (Generic for LCX Family) includes probe and jig capacitance) L ...

Page 7

... Schematic Diagram (Generic for LCX Family) ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 7 www.fairchildsemi.com ...

Page 8

... BQX Leader (Start End) Trailer (Hub End) Tape Dimensions inches (millimeters) Reel Dimensions inches (millimeters) Tape Size A 12mm 13.0 (330.0) 0.059 (1.50) ©1995 Fairchild Semiconductor Corporation 74LCX11 Rev. 1.6.0 Tape Section Number of Cavities 125 (Typ.) Carrier 3000 75 (Typ 0.512 (13.00) 0.795 (20.20) ...

Page 9

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 10

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 11

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 12

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 13

... TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended exhaustive list of all such trademarks. ® ACEx Build it Now™ CorePLUS™ CROSSVOLT™ CTL™ Current Transfer Logic™ ...