en5311qi-e Enpirion, en5311qi-e Datasheet - Page 11

en5311qi-e

Manufacturer Part Number

en5311qi-e

Description

1a Synchronous Buck Regulator With Integrated Inductor

Manufacturer

Enpirion

Datasheet

1.EN5311QI-E.pdf

(16 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Recommendation 3: Multiple small vias (0.25mm after copper plating) should be used to connect

ground terminals of the Input capacitor and the output capacitor to the system ground plane. This

provides a low inductance path for the high-frequency AC currents; thereby reducing ripple and

suppressing EMI (see Fig. 6, Fig. 7, and Fig. 8).

Recommendation 4: The large thermal pad underneath the component must be connected to the

system ground plane through as many thermal vias as possible. The vias should use 0.33mm drill

size with minimum one ounce copper plating (0.035mm plating thickness). This provides the path for

heat dissipation from the converter.

Recommendation 5: The system ground plane referred to in recommendations 3 and 4 should be

the first layer immediately below the surface layer (PCB layer 2). This ground plane should be

continuous and un-interrupted below the converter and the input and output capacitors that carry

large AC currents.

uninterrupted ground “island” should be created on PCB layer 2 immediately underneath the

EN5311QI and its input and output capacitors. The vias that connect the input and output capacitor

grounds, and the thermal pad to the ground island, should continue through to the PCB GND layer as

well.

Recommendation 6: As with any switch-mode DC/DC converter, do not run sensitive signal or

control lines underneath the converter package.

Recommendation 7: The VOUT sense point should be just after the last output filter capacitor next

to the device. Keep the sense trace short in order to avoid noise coupling into the node.

Recommendation 8: Keep R

a high-impedance, sensitive node. Keep the trace to this pin as short as possible. Whenever possible,

connect R

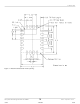

Figure 6 shows an example schematic for the EN5311QI using the internal voltage select. In this

example, the device is set to a VOUT of 1.5V (VS2=0, VS1=1, VS0=1).

Figure 7 shows an example schematic using an external voltage divider. VS0=VS1=VS2= “1”. The

resistor values are chosen to give an output voltage of 2.6V.

Figure 6. Example application, Vout=1.5V.

Figure 8 shows an example board layout. The left side of the figure demonstrates construction of the

PCB top layer. Note the placement of the vias from the input and output filter capacitor grounds, and

©Enpirion 2009 all rights reserved, E&OE

03799

V

(see layout recommendation 3)

IN

ENABLE

b

VS0

VS2

VS1

directly to the GND pin instead of going through the GND plane.

4.7uF

17

18

19

20

If it is not possible to make PCB layer 2 a continuous ground plane, an

10μF

10

9

8

7

a

, C

NC

NC

NC

V

OUT

a

, and R

V

OUT

b

close to the VFB pin (see Figures 4 and 5). The VFB pin is

Figure 7. Example Application, external divider, Vout = 2.6V.

11/24/2009

11

(see layout recommendation 3)

V

IN

ENABLE

VS2

VS1

VS0

4.7uF

17

18

19

20

10μF

10

9

8

7

NC

NC

NC

V

OUT

www.enpirion.com

Ra=200K

Rb=60K

V

OUT

EN5311QI

Rev:B