gl850g Genesys Logic, gl850g Datasheet - Page 16

gl850g

Manufacturer Part Number

gl850g

Description

Gl850g Usb 2.0 Low-power Hub Controller

Manufacturer

Genesys Logic

Datasheet

1.GL850G.pdf

(29 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

GL850G

Manufacturer:

GENESYS

Quantity:

354

Part Number:

GL850G

Manufacturer:

GENESYS

Quantity:

20 000

Part Number:

gl850g-03G

Manufacturer:

GENESYSLOGIC

Quantity:

20 000

Company:

Part Number:

gl850g-13G

Manufacturer:

GENESYS

Quantity:

3 400

Company:

Part Number:

gl850g-21G

Manufacturer:

MPS

Quantity:

2 300

Company:

Part Number:

gl850g-22G

Manufacturer:

I-CubeInc

Quantity:

81

Part Number:

gl850g-22G

Manufacturer:

GENESYS

Quantity:

20 000

Part Number:

gl850g-HHY22

Manufacturer:

GENESYS

Quantity:

20 000

Company:

Part Number:

gl850g-MNG

Manufacturer:

GENESYS

Quantity:

7

Part Number:

gl850g-MNG

Manufacturer:

GENESYS

Quantity:

20 000

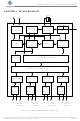

CHAPTER 5 FUNCTION DESCRIPTION

5.1 General

©2000-2008 Genesys Logic Inc. - All rights reserved.

USPORT (upstream port) transceiver is the analog circuit that supports both full-speed and high-speed

electrical characteristics defined in chapter 7 of USB specification Revision 2.0. USPORT transceiver will

operate in full-speed electrical signaling when GL850G is plugged into a 1.1 host/hub. USPORT transceiver

will operate in high-speed electrical signaling when GL850G is plugged into a 2.0 host/hub.

GL850G contains a 40x PLL. PLL generates the clock sources for the whole chip. The generated clocks are

proven quite accurate that help in generating high speed signal without jitter.

This module implements hub (micro)frame timer. The (micro)frame timer is derived from the hub’s local

clock and is synchronized to the host (micro)frame period by the host generated Start of (micro)frame

(SOF). FRTIMER keeps tracking the host’s SOF such that GL850G is always safely synchronized to the

host. The functionality of FRTIMER is described in section 11.2 of USB Specification Revision 2.0.

It operates at 6MIPS of 12Mhz clock to decode the USB command issued from host and then prepares the

data to respond to the host. In addition, C can handle GPIO (general purpose I/O) settings and reading

content of EEPROM to support high flexibility for customers of different configurations of hub. These

configurations include self/bus power mode setting, individual/gang mode setting, downstream port number

setting, device removable/non-removable setting, and PID/VID setting.

UTMI handles the low level USB protocol and signaling. It’s designed based on the Intel’s UTMI

specification 1.01. The major functions of UTMI logic are to handle the data and clock recovery, NRZI

encoding/decoding, Bit stuffing /de-stuffing, supporting USB 2.0 test modes, and serial/parallel conversion.

USPORT implements the upstream port logic defined in section 11.6 of USB specification Revision 2.0. It

mainly manipulates traffics in the upstream direction. The main functions include the state machines of

Receiver and Transmitter, interfaces between UTMI and SIE, and traffic control to/from the REPEATER

and TT.

SIE handles the USB protocol defined in chapter 8 of USB specification Revision 2.0. It co-works with

to play the role of the hub kernel. The main functions of SIE include the state machine of USB protocol

flow, CRC check, PID error check, and timeout check. Unlike USB 1.1, bit stuffing/de-stuffing is

implemented in UTMI, not in SIE.

Control/Status register is the interface register between hardware and firmware. This register contains the

information necessary to control endpoint0 and endpoint1 pipelines. Through the firmware based

architecture, GL850G possesses higher flexibility to control the USB protocol easily and correctly.

Repeater logic implements the control logic defined in section 11.4 and section 11.7 of USB specification

Revision 2.0. REPEATER controls the traffic flow when upstream port and downstream port are signaling

in the same speed. In addition, REPEATER will generate internal resume signal whenever a wakeup event

is issued under the situation that hub is globally suspended.

5.1.1 USPORT Transceiver

5.1.2 PLL (Phase Lock Loop)

5.1.3 FRTIMER

5.1.4 µC

5.1.5 UTMI (USB 2.0 Transceiver Macrocell Interface)

5.1.6 USPORT logic

5.1.7 SIE (Serial Interface Engine)

5.1.8 Control/Status register

5.1.9 REPEATER

C is the micro-processor unit of GL850G. It is an 8-bit RISC processor with 2K ROM and 64 bytes RAM.

GL850G USB 2.0 Low-Power HUB Controller

Page 16

Μ

c