SC16C2550B_07 PHILIPS [NXP Semiconductors], SC16C2550B_07 Datasheet - Page 27

SC16C2550B_07

Manufacturer Part Number

SC16C2550B_07

Description

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 16-byte FIFOs

Manufacturer

PHILIPS [NXP Semiconductors]

Datasheet

1.SC16C2550B_07.pdf

(43 pages)

- Current page: 27 of 43

- Download datasheet (212Kb)

NXP Semiconductors

Table 25.

T

[1]

[2]

[3]

SC16C2550B_4

Product data sheet

Symbol

t

t

N

28d

RESET

amb

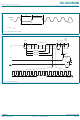

Fig 8. General write timing

Applies to external clock, crystal oscillator max 24 MHz.

Maximum frequency =

RCLK is an internal signal derived from divisor latch LSB (DLL) and divisor latch MSB (DLM) divisor latches.

= 40 C to +85 C; tolerance of V

Parameter

delay from start to reset

TXRDY

RESET pulse width

baud rate divisor

D0 to D7

Dynamic characteristics

A0 to A2

IOW

CSx

10.1 Timing diagrams

-------

t

3w

1

t

6s

t

13d

…continued

CC

Conditions

address

valid

active

10 %; unless otherwise specified.

active

t

13w

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 16-byte FIFOs

Rev. 04 — 15 February 2007

t

16s

data

t

t

16h

t

[3]

13h

6h

Min

200

V

1

-

CC

t

15d

= 2.5 V

(2

8T

Max

16

RCLK

-

1)

Min

40

V

1

-

CC

= 3.3 V

(2

8T

Max

16

RCLK

-

SC16C2550B

1)

Min

40

V

1

-

CC

© NXP B.V. 2007. All rights reserved.

002aaa109

= 5.0 V

(2

8T

Max

16

RCLK

-

1)

27 of 43

Unit

s

ns

Related parts for SC16C2550B_07

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

General purpose CMOS timer

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.) with 16-byte FIFOs

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

Voltage regulator diodes

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

XA 16-bit microcontroller family 32K/512 OTP/ROM/ROMless, watchdog, 2 UARTs

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

5 V, 3.3 V and 2.5 V UART with 32-byte FIFOs and infrared (IrDA) encoder/decoder

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

5V, 3.3 V and 2.5V dual UART, 5 Mbit/s (max.),with 32-byte FIFOs and infrared(IrDA) encoder/decoder

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.), with 64-byte FIFOs and infrared (IrDA) encoder/decoder

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

Single UART with I2C-bus/SPI interface, 64 bytes of transmit and receive FIFOs, IrDA SIR built-in support

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

Master I-2C - bus controller with UART interface

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

BTL stereo Class-D audio amplifier with I2S input

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

3.4 W PDM input class-D audio amplifier

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

TRIODE FOR USE AS GROUNDED GRID U.H.F. AMPLIFIER

Manufacturer:

PHILIPS [NXP Semiconductors]

Datasheet:

Part Number:

Description:

Specific Thales (NXP : BLA0912-250,112)

Manufacturer:

Philips Semiconductors

Part Number:

Description:

Specific Thales (NXP : MX0912B251Y,114)

Manufacturer:

Philips Semiconductors

Part Number:

Description:

Specific Thales (NXP : MX0912B351Y,114)

Manufacturer:

Philips Semiconductors