SAA7113 Philips Semiconductors, SAA7113 Datasheet - Page 51

SAA7113

Manufacturer Part Number

SAA7113

Description

9-bit video input processor

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7113.pdf

(80 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

SAA7113

Manufacturer:

台湾明智类比

Quantity:

20 000

Part Number:

SAA7113H

Manufacturer:

PHILIPS

Quantity:

20 000

Company:

Part Number:

SAA7113H/V2

Manufacturer:

NXP

Quantity:

12 000

Part Number:

SAA7113H/V2

Manufacturer:

NXP/恩智浦

Quantity:

20 000

Company:

Part Number:

SAA7113H/V2,518

Manufacturer:

Sigma Designs Inc

Quantity:

10 000

Philips Semiconductors

15.2

The I

Subaddresses 14H, 18H to 1EH, 20H to 3FH and

63H to FFH are reserved.

15.2.1

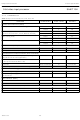

Table 25 Chip version SA 00

15.2.3

Table 27 Analog control 1 SA 02

Notes

1. Mode select (see Figs 35 to 42).

2. To take full advantage of the YC-modes 6 to 9 the I

1999 Jul 01

Mode 0: CVBS (automatic gain) from AI11 (pin 4)

Mode 1: CVBS (automatic gain) from AI12 (pin 7)

Mode 2: CVBS (automatic gain) from AI21 (pin 43)

Mode 3: CVBS (automatic gain) from AI22 (pin 1)

Mode 4: reserved

Mode 5: reserved

Mode 6: Y (automatic gain) from AI11 (pin 4) + C (gain adjustable via

GAI28 to GAI20) from AI21 (pin 43); note 2

Mode 7: Y (automatic gain) from AI12 (pin 7) + C (gain adjustable via

GAI28 to GAI20) from AI22 (pin 1); note 2

Mode 8: Y (automatic gain) from AI11 (pin 4) + C (gain adapted to Y gain)

from AI21 (pin 43); note 2

Mode 9: Y (automatic gain) from AI12 (pin 7) + C (gain adapted to Y gain)

from AI22 (pin 1); note 2

Modes 10 to 15: reserved

9-bit video input processor

Chip Version (CV)

(full luminance bandwidth).

2

C-bus receiver slave address is 48H/49H.

FUNCTION

I

2

C-bus detail

S

S

UBADDRESS

UBADDRESS

00H (

02H

ID07

CV3

READ ONLY REGISTER

FUNCTION

LOGIC LEVELS

ID06

CV2

ID05

CV1

(1)

)

ID04

CV0

2

C-bus bit BYPS (subaddress 09H, bit 7) should be set to logic 1

51

15.2.2

Table 26 Horizontal increment delay

The programming of the horizontal increment delay is

used to match internal processing delays to the delay of

the ADC. Use recommended position only.

Recommended

Maximum delay

Minimum delay

FUNCTION

No update

position

S

UBADDRESS

MODE 3 MODE 2 MODE 1 MODE 0

0

0

0

0

0

0

0

0

1

1

1

01H

CONTROL BITS D3 TO D0

IDEL3 IDEL2 IDEL1 IDEL0

1

1

1

0

0

0

0

0

1

1

1

1

0

0

1

1

1

0

0

Product specification

SAA7113H

0

0

1

1

0

0

1

1

0

0

1

1

1

0

0

0

1

0

1

0

1

0

1

0

1

1

1

0

0

0