HD6433045 HITACHI [Hitachi Semiconductor], HD6433045 Datasheet - Page 210

HD6433045

Manufacturer Part Number

HD6433045

Description

Hitachi Single-Chip Microcomputer

Manufacturer

HITACHI [Hitachi Semiconductor]

Datasheet

1.HD6433045.pdf

(867 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD6433045A58F

Manufacturer:

PWRT

Quantity:

4 172

Part Number:

HD6433045SA28FV

Manufacturer:

RENESAS/瑞萨

Quantity:

20 000

- Current page: 210 of 867

- Download datasheet (3Mb)

8.3 Register Descriptions (Full Address Mode)

In full address mode the A and B channels operate together. Full address mode is selected as

indicated in table 8-4.

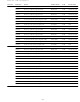

8.3.1 Memory Address Registers (MAR)

A memory address register (MAR) is a 32-bit readable/writable register. MARA functions as the

source address register of the transfer, and MARB as the destination address register.

An MAR consists of four 8-bit registers designated MARR, MARE, MARH, and MARL. All bits

of MARR are reserved: they cannot be modified and are always read as 1.

The MAR value is incremented or decremented each time one byte or word is transferred,

automatically updating the source or destination memory address. For details, see section 8.3.4,

Data Transfer Control Registers (DTCR).

The MARs are not initialized by a reset or in standby mode.

8.3.2 I/O Address Registers (IOAR)

The I/O address registers (IOARs) are not used in full address mode.

Bit

Initial value

Read/Write

31

—

1

30

—

1

29

—

1

MARR

28

—

1

27

—

1

26

—

1

25

—

1

24

—

1

R/W

23

R/W

22

R/W

21

R/W

MARE

20

Source or destination address

R/W

19

R/W

18

196

R/W

17

Undetermined

R/W

16

R/W

15

R/W

14

R/W

13

R/W

MARH

12

R/W

11

R/W

10

R/W

9

R/W

8

R/W

7

R/W

6

R/W

5

R/W

MARL

4

R/W

3

R/W

2

R/W

1

R/W

0

Related parts for HD6433045

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

LOW FREQUENCY POWER AMPLIFIER

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON N-CHANNEL JUNCTION FET LOW FREQUECY LOW NOISE AMPLIFIER

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON SPEED POWER SWITCHING

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON P-CHANNEL MOS FET HIGH SPEED POWER SWITCHING

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON P-CHANNEL MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON P-CHANNEL MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet: