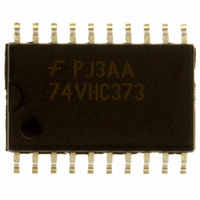

74VHC373M Fairchild Semiconductor, 74VHC373M Datasheet

74VHC373M

Specifications of 74VHC373M

Available stocks

Related parts for 74VHC373M

74VHC373M Summary of contents

Page 1

... Order Number Number 74VHC373M M20B 74VHC373SJ M20D 74VHC373MTC MTC20 Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter “X” to the ordering number. Pb-Free package per JEDEC J-STD-020B. Connection Diagram ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 ...

Page 2

... Latch Enable Logic Diagram Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays. ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 Functional Description The VHC373 contains eight D-type latches with 3-STATE standard outputs. When the Latch Enable (LE) input is HIGH, data on the D In this condition the latches are transparent, i ...

Page 3

... Operating Temperature OPR Input Rise and Fall Time 3.3V ± 0. 5.0V ± 0. Note: 1. Unused inputs must be held HIGH or LOW. They may not float. ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 Parameter (1) Parameter 3 Rating –0.5V to +7.0V –0.5V to +7.0V –0. 0.5V CC –20mA ±20mA ±25mA ± ...

Page 4

... OL (2) V Quiet Output Minimum OLV Dynamic V OL (2) V Minimum HIGH Level IHD Dynamic Input Voltage (2) V Maximum LOW Level ILD Dynamic Input Voltage Note: 2. Parameter guaranteed by design. ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 (V) Conditions Min. 1.50 0 –50µ 1 2.9 IL 4.4 = – ...

Page 5

... calculated by the equation Operating Requirements Symbol Parameter t (H) Minimum Pulse Width W (LE) t Minimum Set-Up Time S t Minimum Hold Time H ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 V (V) Conditions CC = 15pF 3.3 ± 0 50pF 15pF 5.0 ± 0 50pF 15pF 3.3 ± 0.3 ...

Page 6

... Physical Dimensions Dimensions are in inches (millimeters) unless otherwise noted. Figure 2. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 Package Number M20B 6 www.fairchildsemi.com ...

Page 7

... Physical Dimensions (Continued) Dimensions are in millimeters unless otherwise noted. Figure 3. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 Package Number M20D 7 www.fairchildsemi.com ...

Page 8

... Physical Dimensions (Continued) Dimensions are in millimeters unless otherwise noted. Figure 4. 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide ©1993 Fairchild Semiconductor Corporation 74VHC373 Rev. 1.3 Package Number MTC20 8 www.fairchildsemi.com ...

Page 9

... TRADEMARKS The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended exhaustive list of all such trademarks. ® ACEx Across the board. Around the world. ActiveArray Bottomless Build it Now CoolFET CROSSVOLT CTL™ Current Transfer Logic™ ...