XE8000EV108 Semtech, XE8000EV108 Datasheet - Page 92

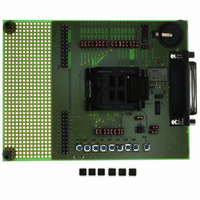

XE8000EV108

Manufacturer Part Number

XE8000EV108

Description

EVAL BOARD FOR XE8806/XE8807

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV108

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC06AMI026

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 92 of 143

- Download datasheet (889Kb)

If RfifEnCod in register RegRfifCmd2 is set to 1, the bit stream coming from the shift register is encoded first

before sending it to the RFIF3 pin. The type of protocol is selected using the RfifPCM[2:0] control word in the

register RegRfifCmd2. The selection control bits are given in Table 14-14.

PCM Codes

When the bit RfifEnCod is modified while a transmission is active, the modification will take effect only when a new

byte is loaded from the FIFO into the shift register.

While the encoder is enabled, it is not possible to send a protocol violation as a start pattern. If a protocol violation

is used as a start sequence in the Manchester or Miller protocol, the following sequence should be used:

Beware that in the case a protocol violation is used as a start sequence in Manchester-level or Miller coding, the

used violation will depend on the value of the first bit of the message. As an example: if the Manchester level

coding is used and the first bit of the message is a 0 (encoded 01), the start sequence needs to be a series of 1’s.

If a series of 0’s would be used, the receiver would be unable to distinguish the leading 0 of the message from the

start sequence.

When the encoder is bypassed (RfifEnCod = 0), bits RfifPCM[2:0] still have an influence on the output bit stream :

when the NRZ coding is chosen, the bits are shifted out at the selected bit rate. If the Manchester or Miller codes

are selected however, the bits are shifted out at twice the data rate. This allows the use of two bits in the FIFO to

encode the bits by software.

14.9.4

If required, a bit synchronization clock can be generated on the pin RFIF2 if the data is uncoded or if the NRZ

coding is used (bits RfifEnCod and RfifPCM[2:0] in RegRfifCmd2). To generate this clock, the bit RfifTxClock in

RegRfifCmd2 has to be set. The timing of the generated clock is shown in Figure 14-7.

© Semtech 2006

RfifPCM[2:0]

1) wait until the transmission FIFO is empty (which means the last byte of the preceding message is being

2) clear RfifEnCod,

3) write the uncoded start pattern to the transmission FIFO

4) wait until the transmission FIFO is empty (which means the last byte of the uncoded start pattern is being

5) set RfifEnCod

6) write the message bytes to the FIFO

7) back to 1.

coded and sent),

sent)

Transmission synchronization clock

Level

000

Mark

NRZ

001

Table 14-16: PCM code selection

Space

010

14-12

Level

011

Bi-Phase/Manchester

Mark

100

Space

101

XE8806A/XE8807A

Miller

11X

www.semtech.com

Related parts for XE8000EV108

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: