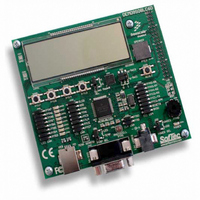

DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet

DEMO9S08LC60

Specifications of DEMO9S08LC60

Related parts for DEMO9S08LC60

DEMO9S08LC60 Summary of contents

Page 1

MC9S08LC60 MC9S08LC36 Data Sheet: Technical Data HCS08 Microcontrollers MC9S08LC60 Rev. 4 07/2007 freescale.com ...

Page 2

...

Page 3

MC9S08LC60 Series Features 8-Bit HCS08 Central Processor Unit (CPU) • 40-MHz HCS08 CPU • HC08 instruction set with added BGND instruction • Background debugging system • Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints ...

Page 4

...

Page 5

... MC9S08LC60 Series Data Sheet This document contains information on a new product. Specifications and information herein are subject to change without notice. Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2007. All rights reserved. Covers MC9S08LC60 ...

Page 6

... Updated the Appendix with ESD tables, package info, and mechanical drawings for 4 07/2007 the 80-pin LQFP package. This product incorporates SuperFlash Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2007. All rights reserved. MC9S08LC60 Series Data Sheet: Technical Data, Rev Description of Changes ® ...

Page 7

... Inter-Integrated Circuit (S08IICV1) ............................................... 249 Chapter 15 Analog-to-Digital Converter (S08ADC12V1)................................ 267 Chapter 16 Analog Comparator (S08ACMPV2) .............................................. 293 Chapter 17 Development Support ................................................................... 301 Appendix A Electrical Characteristics.............................................................. 323 Appendix B Ordering Information and Mechanical Drawings........................ 351 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor List of Chapters Title Page 7 ...

Page 8

...

Page 9

... LVD Enabled in Stop Mode ............................................................................36 3.6.1.2 Active BDM Enabled in Stop Mode ...............................................................36 3.6.2 Stop2 Mode ....................................................................................................................36 3.6.3 Stop1 Mode ....................................................................................................................37 3.6.4 On-Chip Peripheral Modules in Stop Modes .................................................................37 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table of Contents Title Chapter 1 Device Overview Chapter 2 Pins and Connections , ...............................................................................29 ...

Page 10

... Real-Time Interrupt (RTI) ...............................................................................................................69 5.8 Reset, Interrupt, and System Control Registers and Control Bits ...................................................70 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC) .........................................70 5.8.2 System Reset Status Register (SRS) ...............................................................................72 MC9S08LC60 Series Data Sheet: Technical Data, Rev Title Chapter 4 Memory Chapter 5 Page Freescale Semiconductor ...

Page 11

... Introduction .....................................................................................................................................95 7.1.1 Features ...........................................................................................................................97 7.1.2 Modes of Operation ........................................................................................................97 7.1.2.1 KBI in Wait Mode ...........................................................................................97 7.1.2.2 KBI in Stop Modes .........................................................................................97 7.1.2.3 KBI in Active Background Mode ...................................................................97 7.1.3 Block Diagram ................................................................................................................97 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Title Chapter 6 Parallel Input/Output Chapter 7 Keyboard Interrupt (S08KBIV2) Page 11 ...

Page 12

... Special Operations .........................................................................................................................109 8.4.1 Reset Sequence .............................................................................................................109 8.4.2 Interrupt Sequence ........................................................................................................109 8.4.3 Wait Mode Operation ...................................................................................................110 8.4.4 Stop Mode Operation ...................................................................................................110 8.4.5 BGND Instruction ........................................................................................................111 8.5 HCS08 Instruction Set Summary ..................................................................................................112 MC9S08LC60 Series Data Sheet: Technical Data, Rev Title Chapter 8 Page Freescale Semiconductor ...

Page 13

... LCD Power Supply and Voltage Buffer Configuration .................................153 9.4.5 Resets ............................................................................................................................155 9.4.6 Interrupts .......................................................................................................................155 9.5 Initialization Section .....................................................................................................................155 9.5.1 Initialization Sequence .................................................................................................156 9.5.2 Initialization Examples .................................................................................................157 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Title Chapter 9 ........................................................................................................127 LL3 Page 13 ...

Page 14

... FLL Engaged Internal Locked ......................................................................................183 10.5.6 FLL Bypassed, External Clock (FBE) Mode ...............................................................183 10.5.7 FLL Engaged, External Clock (FEE) Mode .................................................................183 10.5.7.1 FLL Engaged External Unlocked .................................................................184 10.5.7.2 FLL Engaged External Locked .....................................................................184 MC9S08LC60 Series Data Sheet: Technical Data, Rev Title Chapter 10 Page Freescale Semiconductor ...

Page 15

... Timer Overflow Interrupt Description ..........................................................................211 11.5.3 Channel Event Interrupt Description ............................................................................212 11.5.4 PWM End-of-Duty-Cycle Events .................................................................................212 Serial Communications Interface (S08SCIV3) 12.1 Introduction ...................................................................................................................................213 12.1.1 Features .........................................................................................................................216 12.1.2 Modes of Operation ......................................................................................................216 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Title Chapter 11 Chapter 12 Page 15 ...

Page 16

... SPI Control Register 1 (SPIxC1) ..................................................................................239 13.4.2 SPI Control Register 2 (SPIxC2) ..................................................................................240 13.4.3 SPI Baud Rate Register (SPIxBR) ...............................................................................241 13.4.4 SPI Status Register (SPIxS) ..........................................................................................242 13.4.5 SPI Data Register (SPIxD) ...........................................................................................243 MC9S08LC60 Series Data Sheet: Technical Data, Rev Title Chapter 13 Page Freescale Semiconductor ...

Page 17

... Arbitration Lost Interrupt .............................................................................................263 14.7 Initialization/Application Information ..........................................................................................264 Analog-to-Digital Converter (S08ADC12V1) 15.1 Introduction ...................................................................................................................................267 15.1.1 ADC Configuration Information ..................................................................................267 15.1.1.1 Channel Assignments ....................................................................................267 15.1.1.2 Alternate Clock .............................................................................................268 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Title Chapter 14 Chapter 15 Page 17 ...

Page 18

... Initialization Information ..............................................................................................................286 15.5.1 ADC Module Initialization Example ...........................................................................286 15.5.1.1 Initialization Sequence ..................................................................................286 15.5.1.2 Pseudo — Code Example .............................................................................287 15.6 Application Information ................................................................................................................288 MC9S08LC60 Series Data Sheet: Technical Data, Rev Title ) ................................................................................................272 DDAD ) ..............................................................................................272 SSAD ) .................................................................................272 REFH ) ..................................................................................272 REFL Page Freescale Semiconductor ...

Page 19

... Bus Capture Information and FIFO Operation .............................................................310 17.3.3 Change-of-Flow Information ........................................................................................311 17.3.4 Tag vs. Force Breakpoints and Triggers .......................................................................311 17.3.5 Trigger Modes ..............................................................................................................312 17.3.6 Hardware Breakpoints ..................................................................................................314 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Title Chapter 16 Chapter 17 Development Support Page 19 ...

Page 20

... A.12 EMC Performance .........................................................................................................................348 A.12.1 Radiated Emissions .........................................................................................................348 A.12.2 Conducted Transient Susceptibility ................................................................................349 Ordering Information and Mechanical Drawings B.1 Ordering Information ....................................................................................................................351 B.2 Mechanical Drawings ....................................................................................................................351 MC9S08LC60 Series Data Sheet: Technical Data, Rev Title Appendix A Electrical Characteristics Appendix B Page Freescale Semiconductor ...

Page 21

... MC9S08LC60 Series and summarizes the differences among them. Table 1-1. Devices in the MC9S08LC60 Series Device MC9S08LC60 MC9S08LC36 I/O pins (max) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor FLASH A FLASH B 32K 28K 24K 12K Table 1-2. Package Options by Feature ...

Page 22

... FP[39:32], PTA[1:0], and PTA[7:4] are not available in the 64 LQFP. 9. ACMPO is not available. PTA[7:4]/KBI1P[7:4]/ADP[7:4] PTA3/KBI1P3/ADP3/ACMP– PTA2/KBI1P2/ADP2/ACMP+ PTA[1:0]/KBI1P[1:0]/ADP[1:0] PTB7/KBI2P4/SS1 PTB6/KBI2P3/SPSCK1 PTB5/MOSI1/SCL PTB4/MISO1/SDA PTB3/KBI2P2 PTB2/RESET PTB1/KBI2P1/XTAL PTB0/KBI2P0/EXTAL PTC7/KBI2P7/IRQ/TPMCLK PTC6/BKGD/MS PTC5/KBI2P6/TPM2CH1 PTC4/KBI2P5/TPM2CH0 PTC3/SS2/TPM1CH1 PTC2/SPSCK2/TPM1CH0 PTC1/MOSI2/TxD PTC0/MISO2/RxD . IRQ should not be driven above Freescale Semiconductor ...

Page 23

... The external crystal oscillator — An external clock source — The output of the digitally-controlled oscillator (DCO) in the frequency-locked loop sub-module MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 1-3. Module Versions Module Analog Comparator (ACMP) Analog-to-Digital Converter (ADC) Internal Clock Generator (ICG) ...

Page 24

... ICGLCLK — Development tools can select this internal self-clocked source (~ 8 MHz) to speed up BDC communications in systems where the bus clock is slow. • ICGERCLK — External reference clock can be selected as the real-time interrupt clock source. MC9S08LC60 Series Data Sheet: Technical Data, Rev Freescale Semiconductor ...

Page 25

... This section describes signals that connect to package pins. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals. 2.2 Device Pin Assignment Figure 2-1 and Figure 2-2 show the pin assignments for the MC9S08LC60 Series devices in its available packages. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 25 ...

Page 26

... Figure 2-1. MC9S08LC60 Series in 80-Pin LQFP Package MC9S08LC60 Series Data Sheet: Technical Data, Rev MC9S08LC60 Series 50 80-Pin LQFP FP27 FP28 FP29 FP30 FP31 FP32 FP33 FP34 FP35 FP36 FP37 FP38 FP39 PTC7/KBI2P7/IRQ/TPMCLK PTC6/ BKGD/MS PTC5/KBI2P6/TPM2CH1 PTC4/KBI2P5/TPM2CH0 PTC3/SS2/TPM1CH1 PTC2/SPSCK2/TPM1CH0 PTC1/MOSI2/TxD Freescale Semiconductor ...

Page 27

... MC9S08LC60 Series application systems in the 80-pin package. Connections will be similar to the 64-pin package except for the number of I/O pins available. A more detailed discussion of system connections follows. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor ...

Page 28

... REFL DDAD and V can be LCD LL1 LL2 LL3 powered internally using externally based on software configuration of the LCD module. (Shown as internally powered “no connect” when the LCD LCD module is being powered via filter on RESET is recommended for EMC-sensitive applications. Freescale Semiconductor to ) REFH . ...

Page 29

... C1 and C2. The crystal manufacturer typically specifies a load capacitance which is the series combination of C1 and C2 which are usually the same size first-order approximation, use estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL). MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor , DDAD ...

Page 30

... Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin. MC9S08LC60 Series Data Sheet: Technical Data, Rev released, and sampled again approximately 38 Self_reset Figure 2-3 for Freescale Semiconductor ...

Page 31

... To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor , and V pins are dedicated to providing power to the LCD module. cap1 cap2 Chapter 6, “ ...

Page 32

... FP37 — FP36 — FP35 — FP34 — FP33 — FP32 39 FP31 40 FP30 41 FP29 42 FP28 43 FP27 44 FP26 45 FP25 46 FP24 47 FP23 48 FP22 49 FP21 50 FP20 51 FP19 52 FP18 53 FP17 54 FP16 55 FP15 56 FP14 57 FP13 58 FP12 59 FP11 60 FP10 61 FP9 62 FP8 63 FP7 Freescale Semiconductor Alt3 TPMCLK ...

Page 33

... When the BKGD/MS pin is low at the time the MCU exits reset • When a BACKGROUND command is received through the BKGD pin • When a BGND instruction is executed • When encountering a BDC breakpoint • When encountering a DBG breakpoint MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 33 ...

Page 34

... MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from wait mode and enter active background mode. MC9S08LC60 Series Data Sheet: Technical Data, Rev Development Support chapter. Freescale Semiconductor ...

Page 35

... Power consumption is lower when the 1-kHz source is disabled, but in that case the real-time interrupt cannot wake the MCU from stop. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 3-1. Stop Mode Selection PDC ...

Page 36

... I/O port registers, which have been saved in RAM, to the port registers MC9S08LC60 Series Data Sheet: Technical Data, Rev chapter of this data sheet. If ENBDM is set when the CPU NOTE Table 3-1. Most is below the LVD DD Freescale Semiconductor ...

Page 37

... Refer to Mode,” Section 3.6.2, “Stop2 Mode,” and behavior in stop modes. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor NOTE Section 3.6.1, “Stop3 Mode,” for specific information on system Chapter 3 Modes of Operation Table 3-1 ...

Page 38

... Off Off Off Off Off Off Off Off Off Off Off Off Off Off Off Off Off Off Off Standby Hi-Z States Held Stop3 Standby Standby Standby Standby 1 Optionally On Standby 2 Optionally On Standby 3 Optionally On Standby Standby Standby Standby States Held Freescale Semiconductor ...

Page 39

... I/O and control/status registers. The registers are divided into three groups: • Direct-page registers (0x0000 through 0x005F) • High-page registers (0x1800 through 0x186F) • Nonvolatile registers (0xFFB0 through 0xFFBF) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 39 ...

Page 40

... BYTES 0xFFFF MC9S08LC36 Table 4-1. Reset and Interrupt Vectors Vector Unused Vector Space (available for user program) LCD 0x0000 0x005F 0x0060 RAM 0x0A5F 0x0A60 0x17FF 0x1800 0x186F 0x1870 0x486F 0x4870 0x9FFF 0xA000 0xFFFF Chapter 5, “Resets, Vector Name Vlcd Freescale Semiconductor ...

Page 41

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 4-1. Reset and Interrupt Vectors Vector RTI IIC ACMP ADC Conversion Keyboard 2 Keyboard 1 SCI Transmit ...

Page 42

... MC9S08LC60 Series Data Sheet: Technical Data, Rev can use the more efficient direct addressing mode which only and Table 4-4 the whole address in column one is shown in bold. In 4-4, the register names in column two are shown in bold to set them apart Table 4 summary of all Freescale Semiconductor ...

Page 43

... TIE 0x0024 SCIS1 TDRE 0x0025 SCIS2 0 0x0026 SCIC3 R8 0x0027 SCID Bit 7 0x0028 SPI1C1 SPIE 0x0029 SPI1C2 0 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor PTAD6 PTAD5 PTAD4 PTADD6 PTADD5 PTADD4 PTBD6 PTBD5 PTBD4 PTBDD6 PTBDD5 PTBDD4 PTCD6 PTCD5 PTCD4 PTCDD6 ...

Page 44

... CLKSA PS2 PS1 Freescale Semiconductor Bit 0 SPR0 0 0 Bit LSBFE SPC0 SPR0 0 0 Bit ICGIF DCOS 0 PS0 Bit 8 Bit 0 Bit 8 Bit 0 0 Bit 8 Bit 0 0 Bit 8 Bit 0 — ...

Page 45

... DBGC DBGEN 0x1817 DBGT TRGSEL 0x1818 DBGS AF 0x1819– Reserved — 0x181F 0x1820 FCDIV DIVLD 0x1821 FOPT KEYEN 0x1822 Reserved — 0x1823 FCNFG 0 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor CH0IE MS0B MS0A CH1IE MS1B MS1A — — ...

Page 46

... FP28BP3 FP28BP2 FP28BP1 FP30BP3 FP30BP2 FP30BP1 FP32BP3 FP32BP2 FP32BP1 FP34BP3 FP34BP2 FP34BP1 FP36BP3 FP36BP2 FP36BP1 FP38BP3 FP38BP2 FP38BP1 FP40BP3 FP40BP2 FP40BP1 Freescale Semiconductor Bit 0 FPDIS 0 FCMD0 — — PTAPE0 PTASE0 PTADS0 0 PTBPE0 PTBSE0 PTBDS0 0 PTCPE0 PTCSE0 PTCDS0 — DUTY0 LCDSTP3 FP0EN ...

Page 47

... KEYEN 1 Freescale Semiconductor provides a factory trim to set the FIRG to 243 kHz. If user code changes the value of the NVICGTRM register, the factory trim value will be lost. User code should save the content of NVICGTRM before any mass erase operation. Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security ...

Page 48

... For a more detailed discussion of in-circuit and in-application programming, refer to the HCS08 Family Reference Manual, Volume I, Freescale Semiconductor document order number HCS08RMv1/D. Because the MC9S08LC60 Series contains two FLASH arrays, program and erase operations can be conducted on one array while executing code from the other ...

Page 49

... Parameter Byte program Byte program (burst) Page erase Mass erase 1 Excluding start/end overhead MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor (FCDIV)). This register can be written only ) is used by the command processor to time FCLK = 1/f FCLK FCLK FCLK Table 4-5. Program and Erase Times ...

Page 50

... The command sequence must be completed by clearing FCBEF to launch the command. burst programming. The FCDIV register must be initialized before using any FLASH commands. MC9S08LC60 Series Data Sheet: Technical Data, Rev NOTE Figure 4 flowchart for executing all of the commands except for Freescale Semiconductor ...

Page 51

... A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor (Note 1) Note 1: Required only once after reset. WRITE TO FCDIV ...

Page 52

... TO BUFFER ADDRESS AND DATA WRITE COMMAND (0x25) TO FCMD WRITE 1 TO FCBEF Note 2: Wait at least four bus cycles before TO LAUNCH COMMAND (Note 2) AND CLEAR FCBEF YES FPVIO OR FACCERR ? NO YES NEW BURST COMMAND ? NO 0 FCCF ? 1 DONE checking FCBEF or FCCF. ERROR EXIT Freescale Semiconductor ...

Page 53

... FPS bits must be set to 1101 111 which results in the value 0xDFFF as the last address of unprotected memory. In addition to programming the FPS bits to the appropriate value, FPDIS (bit 0 of MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor NVPROT)”). Figure 4-4 ...

Page 54

... NVOPT location which can be done at the same time the FLASH memory is programmed. The 1:0 state disengages security while the other three combinations engage security. Notice the erased state (1:1) MC9S08LC60 Series Data Sheet: Technical Data, Rev A12 A11 A10 A9 A8 Figure 4-4. Block Protection Mechanism Freescale Semiconductor ...

Page 55

... Mass erase FLASH, if necessary. 3. Blank check FLASH. Provided FLASH is completely erased, security is disengaged until the next reset. To avoid returning to secure mode after the next reset, program NVOPT so SEC01:SEC00 = 1:0. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 4 Memory 55 ...

Page 56

... Table 4-6. FCDIV Field Descriptions Description Equation 4-1 and Equation 4-2. Table 4-7 ÷ ([DIV5:DIV0 FCLK Bus ÷ (8 × ([DIV5:DIV0 FCLK Bus 2 1 DIV2 DIV1 DIV0 0 0 shows the appropriate values for PRDIV8 and Eqn. 4-1 Eqn. 4-2 Freescale Semiconductor 0 0 ...

Page 57

... MCU is secure, the contents of RAM and FLASH memory cannot be accessed by instructions from any unsecured source including the background debug interface. For more detailed information about security, refer to Section 4.5, “Security.” MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 4-7. FLASH Clock Divider Settings DIV5:DIV0 (Decimal ...

Page 58

... To change the data flash block protection that will be loaded during the reset sequence, the MC9S08LC60 Series Data Sheet: Technical Data, Rev Table 4-9. Security States Description 0:0 1 0:1 1:0 unsecured 1 KEYACC Table 4-10. FCNFG Field Descriptions Description Section 4.5, secure secure secure “Security.” Freescale Semiconductor ...

Page 59

... FLASH locations at the high address end of the FLASH. Protected FLASH locations cannot be erased or programmed. 0 FLASH Protection Disable FPDIS 0 FLASH block specified by FPS[7:1] is block protected (program and erase not allowed FLASH block is protected. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor FPS5 FPS4 FPS3 (Note 1) ...

Page 60

... After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0x00FF). MC9S08LC60 Series Data Sheet: Technical Data, Rev FPVIOL FACCERR 0 0 Figure 4-9. FLASH Status Register (FSTAT) Table 4-12. FSTAT Field Descriptions Description FBLANK Section 4.4.5, “Access Freescale Semiconductor Errors.” ...

Page 61

... All other command codes are illegal and generate an access error not necessary to perform a blank check command after a mass erase operation. Blank check is required only as part of the security unlocking mechanism. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Execution” for a detailed discussion of FLASH 5 ...

Page 62

... Chapter 4 Memory MC9S08LC60 Series Data Sheet: Technical Data, Rev Freescale Semiconductor ...

Page 63

... SP is forced to 0x00FF at reset. The MC9S08LC60 Series has seven sources for reset: • Power-on reset (POR) • Low-voltage detect (LVD) • Computer operating properly (COP) timer MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 5-2) 63 ...

Page 64

... Clock Source COPT 0 ~1 kHz 1 ~1 kHz 0 Bus 1 Bus = 1 ms. See t RTI Timing,” for the tolerance of this value. Section 5.8.4, “System (SOPT2),” for additional COP Overflow Count cycles (32 ms cycles (256 ms cycles 18 2 cycles in the appendix RTI Freescale Semiconductor ...

Page 65

... This practice is not recommended for anyone other than the most experienced programmers because it can lead to subtle program errors that are difficult to debug. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration 65 ...

Page 66

... TOWARD LOWER ADDRESSES 7 0 CONDITION CODE REGISTER ACCUMULATOR * INDEX REGISTER (LOW BYTE X) PROGRAM COUNTER HIGH PROGRAM COUNTER LOW TOWARD HIGHER ADDRESSES * High byte (H) of index register is not automatically stacked. Figure 5-1. Interrupt Stack Frame SP AFTER INTERRUPT STACKING SP BEFORE THE INTERRUPT Freescale Semiconductor ...

Page 67

... CCR the CPU will finish the current instruction, stack the PCL, PCH and CCR CPU registers, set the I bit, and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration NOTE . ...

Page 68

... CH1IE TPM2 channel 1 CH0IE TPM2 channel 0 TOIE TPM1 overflow CH1IE TPM1 channel 1 CH0IE TPM1 channel 0 LOLRE/LOCRE ICG LVDIE Low-voltage detect IRQIE IRQ pin — Software interrupt COPE Watchdog timer LVDRE Low-voltage detect — External pin — Illegal opcode Freescale Semiconductor ...

Page 69

... Only the internal 1-kHz clock source can be selected to wake the MCU from stop1 or stop2 modes. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration level. Both the POR bit and the LVD bit in SRS are set ...

Page 70

... MC9S08LC60 Series Data Sheet: Technical Data, Rev Section 5.8.7, “System Real-Time Interrupt Status and Control Chapter 4, “Memory” of this data sheet for the absolute Operation.” IRQF IRQEDG IRQPE 0 0 Table 5-3. IRQSC Field Descriptions Description IRQIE IRQACK Freescale Semiconductor 0 IRQMOD 0 ...

Page 71

... Section 5.5.2.2, “Edge and Level 0 IRQ event on falling edges or rising edges only. 1 IRQ event on falling edges and low levels or on rising edges and high levels. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration Description Sensitivity” ...

Page 72

... PIN COP ILOP Writing any value to SRS address clears COP watchdog timer (1) (1) (1) Note Note Figure 5-3. System Reset Status (SRS) Table 5-4. SRS Field Descriptions Description MC9S08LC60 Series Data Sheet: Technical Data, Rev ICG LVD (1) 0 Note 0 Freescale Semiconductor ...

Page 73

... R COPE COPT W Reset Unimplemented or Reserved Figure 5-5. System Options Register (SOPT1) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration Table 5-5. SBDFR Field Descriptions Description 5 ...

Page 74

... Analog Comparator to Input Capture Enable— This bit connects the output of ACMP to TPM1 input channel 0. ACIC 0 ACMP output not connected to TPM1 input channel 0 1 ACMP output connected to TPM1 input channel 0. MC9S08LC60 Series Data Sheet: Technical Data, Rev Table 5-6. SOPT1 Field Descriptions Description Table 5-7. SOPT2 Field Descriptions Description ACIC Freescale Semiconductor ...

Page 75

... Part Identification Number — Each derivative in the HCS08 Family has a unique identification number. The ID[7:0] MC9S08LC60 Series is hard coded to the value 0x0C. See also ID bits in MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration 5 4 ...

Page 76

... Characteristics,” for the tolerance on these values RTIS2 RTIS External Clock Source Period = t ext Disable RTI t x 256 ext t x 1024 ext t x 2048 ext t x 4096 ext t x 8192 ext t x 16384 ext t x 32768 ext Table A-12 Freescale Semiconductor 0 0 RTIS 0 2 for details. ...

Page 77

... Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the BGBE ADC module on one of its internal channels or the ACMP. 0 Bandgap buffer disabled. 1 Bandgap buffer enabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 5 Resets, Interrupts, and System Configuration ...

Page 78

... Partial Power Down Control — The write-once PPDC bit controls which power down mode, stop1 or stop2, is PPDC selected. 0 Stop1, full power down, mode enabled if PDC set. 1 Stop2, partial power down, mode enabled if PDC set. MC9S08LC60 Series Data Sheet: Technical Data, Rev Modes.” PDF PPDF Table 5-13. SPMSC2 Field Descriptions Description PDC PPDC PPDACK Freescale Semiconductor ...

Page 79

... Low-Voltage Detect Voltage Select — The LVDV bit selects the LVD trip point voltage (V LVDV 0 Low trip point selected (V 1 High trip point selected (V 4 Low-Voltage Warning Voltage Select — The LVWV bit selects the LVW trip point voltage (V LVWV 0 Low trip point selected (V 1 High trip point selected (V Freescale Semiconductor 5 4 LVDV LVWV ...

Page 80

... Chapter 5 Resets, Interrupts, and System Configuration MC9S08LC60 Series Data Sheet: Technical Data, Rev Freescale Semiconductor ...

Page 81

... Reading and writing of parallel I/Os is performed through the port data registers. The direction, either input or output, is controlled through the port data direction registers. The parallel I/O port function for an individual pin is illustrated in the block diagram shown in MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 1-2 for details). See Chapter 2, “Pins and ...

Page 82

... I/O registers. These registers are used to control pullups, slew rate, and drive strength for the pins. See Section 6.2.1, “Port A Registers MC9S08LC60 Series Data Sheet: Technical Data, Rev PTxDDn D Q PTxDn Figure 6-1. Parallel I/O Block Diagram for more information. OUTPUT ENABLE OUTPUT DATA INPUT DATA SYNCHRONIZER Freescale Semiconductor ...

Page 83

... I/O registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Operation” for the absolute address assignments for all parallel Chapter 6 Parallel Input/Output ...

Page 84

... Output driver enabled for port A bit n and PTAD reads return the contents of PTADn. MC9S08LC60 Series Data Sheet: Technical Data, Rev PTAD5 PTAD4 PTAD3 Figure 6-2. Port A Data Register (PTAD) Table 6-1. PTAD Field Descriptions Description PTADD5 PTADD4 PTADD3 Table 6-2. PTADD Field Descriptions Description PTAD2 PTAD1 PTAD0 PTADD2 PTADD1 PTADD0 Freescale Semiconductor ...

Page 85

... A are enabled as KBI inputs and are configured to detect rising edges/high levels, the pullup enable bits enable pulldown rather than pullup devices. 0 Internal pullup device disabled. 1 Internal pullup device enabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor PTAPE PTAPE5 ...

Page 86

... High output drive strength selected for port A bit n. MC9S08LC60 Series Data Sheet: Technical Data, Rev PTASE PTASE5 PTASE4 PTASE3 Table 6-4. PTASE Field Descriptions Description PTADS PTADS5 PTADS4 PTADS3 Table 6-5. PTADS Field Descriptions Description PTASE2 PTASE1 PTASE0 PTADS2 PTADS1 PTADS0 Freescale Semiconductor ...

Page 87

... MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor ...

Page 88

... I/O control logic or any shared peripheral function regardless of the state of the corresponding pullup enable register bit. The pullup device is also disabled if the pin is controlled by an analog function. MC9S08LC60 Series Data Sheet: Technical Data, Rev PTBDD5 PTBDD4 PTBDD3 Table 6-7. PTBDD Field Descriptions Description PTBPE PTBDD2 PTBDD1 PTBDD0 Freescale Semiconductor ...

Page 89

... PTBSE[7:0] determine whether the slew rate controlled outputs are enabled. For port B pins that are configured as inputs, these bits are ignored. 0 Slew rate control disabled. 1 Slew rate control enabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor PTBPE5 PTBPE4 ...

Page 90

... This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses. MC9S08LC60 Series Data Sheet: Technical Data, Rev PTBDS PTBDS5 PTBDS4 PTBDS3 Table 6-10. PTBDS Field Descriptions Description PTBDS2 PTBDS1 PTBDS0 Freescale Semiconductor ...

Page 91

... Associated with the parallel I/O ports is a set of registers located in the high page register space that operate independently of the parallel I/O registers. These registers are used to control pullups, slew rate, and drive MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 5 4 ...

Page 92

... KBI inputs and are configured to detect rising edges/high levels, the pullup enable bits enable pulldown rather than pullup devices. 0 Internal pullup device disabled. 1 Internal pullup device enabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev PTCPE PTCPE5 PTCPE4 PTCPE3 Table 6-13. PTCPE Field Descriptions Description PTCPE2 PTCPE1 PTCPE0 Freescale Semiconductor ...

Page 93

... DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this the EMC emissions may be affected by enabling pins as high drive. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor PTCSE ...

Page 94

... PTC pin. For port C pins that are configured as inputs, these bits have no effect. 0 Low output drive strength selected for port C bit n. 1 High output drive strength selected for port C bit n. MC9S08LC60 Series Data Sheet: Technical Data, Rev PTCDS5 PTCDS4 PTCDS3 Table 6-15. PTCDS Field Descriptions Description PTCDS2 PTCDS1 PTCDS0 Freescale Semiconductor ...

Page 95

... MC9S08LC60 Series MCUs have two KBIs. When they are described individually, they are called KBI1 and/or KBI2. When referring to the module in general or both KBIs collectively, they are called KBIx. Figure 7-1 Shows the MC9S08LC60 Series block guide with the KBIs highlighted. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 95 ...

Page 96

... FP[39:32], PTA[1:0], and PTA[7:4] are not available in the 64 LQFP. 9. ACMPO is not available. PTA[7:4]/KBI1P[7:4]/ADP[7:4] PTA3/KBI1P3/ADP3/ACMP– PTA2/KBI1P2/ADP2/ACMP+ PTA[1:0]/KBI1P[1:0]/ADP[1:0] PTB7/KBI2P4/SS1 PTB6/KBI2P3/SPSCK1 PTB5/MOSI1/SCL PTB4/MISO1/SDA PTB3/KBI2P2 PTB2/RESET PTB1/KBI2P1/XTAL PTB0/KBI2P0/EXTAL PTC7/KBI2P7/IRQ/TPMCLK PTC6/BKGD/MS PTC5/KBI2P6/TPM2CH1 PTC4/KBI2P5/TPM2CH0 PTC3/SS2/TPM1CH1 PTC2/SPSCK2/TPM1CH0 PTC1/MOSI2/TxD PTC0/MISO2/RxD . IRQ should not be driven above Freescale Semiconductor ...

Page 97

... When the microcontroller is in active background mode, the KBI will continue to operate normally. 7.1.3 Block Diagram The block diagram for the keyboard interrupt module is shown MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 7 Keyboard Interrupt (S08KBIV2) Modes of Operation Figure 7-2. ...

Page 98

... The signal properties of KBI are shown in Signal KBIxPn MC9S08LC60 Series Data Sheet: Technical Data, Rev KBACK V RESET DD CLR KEYBOARD INTERRUPT FF KBMOD Table 7-1. Table 7-1. Signal Properties Function Keyboard interrupt pins BUSCLK KBF SYNCHRONIZER STOP BYPASS KBIx STOP INTERRUPT T REQUES KBIE I/O I Freescale Semiconductor ...

Page 99

... Keyboard detects both edges and levels. 7.3.2 KBIx Pin Enable Register (KBIxPE) KBIxPE contains the pin enable control bits. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Memory chapter for the absolute address assignments for ...

Page 100

... KBEDGn bits in the keyboard interrupt edge select register (KBIxES). MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 100 KBIPE5 KBIPE4 KBIPE3 Figure 7-4. KBIx Pin Enable Register Description KBEDG5 KBEDG4 KBEDG3 Figure 7-5. KBIx Edge Select Register Description KBIPE2 KBIPE1 KBIPE0 KBEDG2 KBEDG1 KBEDG0 Freescale Semiconductor ...

Page 101

... If using internal pullup/pulldown device, configure the associated pullup enable bits in PTxPE. 4. Enable the KBI pins by setting the appropriate KBIPEn bits in KBIxPE. 5. Write to KBACK in KBIxSC to clear any false interrupts. 6. Set KBIE in KBIxSC to enable interrupts. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 7 Keyboard Interrupt (S08KBIV2) 101 ...

Page 102

... Chapter 7 Keyboard Interrupt (S08KBIV2) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 102 Freescale Semiconductor ...

Page 103

... This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the HCS08 Family Reference Manual, volume 1, Freescale Semiconductor document order number HCS08RMV1/D. The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler effi ...

Page 104

... X. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 104 7 0 ACCUMULATOR A 16-BIT INDEX REGISTER H:X INDEX REGISTER (LOW STACK POINTER PROGRAM COUNTER CCR CARRY ZERO NEGATIVE INTERRUPT MASK HALF-CARRY (FROM BIT 3) TWO’S COMPLEMENT OVERFLOW Figure 8-1. CPU Registers Freescale Semiconductor ...

Page 105

... For a more detailed explanation of how each instruction sets the CCR bits, refer to the HCS08 Family Reference Manual, volume 1, Freescale Semiconductor document order number HCS08RMv1. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) 105 ...

Page 106

... No carry out of bit 7 1 Carry out of bit 7 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 106 CCR CARRY ZERO NEGATIVE INTERRUPT MASK HALF-CARRY (FROM BIT 3) TWO’S COMPLEMENT OVERFLOW Figure 8-2. Condition Code Register Table 8-1. CCR Register Field Descriptions Description Freescale Semiconductor ...

Page 107

... This is faster and more memory efficient than specifying a complete 16-bit address for the operand. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) 107 ...

Page 108

... SP-Relative, 8-Bit Offset (SP1) This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 108 Freescale Semiconductor ...

Page 109

... After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) Resets, Interrupts, and System Configuration ...

Page 110

... MCU even stop mode. Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 110 chapter for more details. Freescale Semiconductor ...

Page 111

... Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) 111 ...

Page 112

... Two’s complement overflow indicator, bit Half carry, bit Interrupt mask, bit Negative indicator, bit Zero indicator, bit Carry/borrow, bit 0 (carry out of bit 7) CCR activity notation – = Bit not affected MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 112 Table 8-2. Freescale Semiconductor ...

Page 113

... Address modes INH = Inherent (no operands) IMM = 8-bit or 16-bit immediate DIR = 8-bit direct EXT = 16-bit extended MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) 113 ...

Page 114

... IMM AB ii DIR BB dd EXT IX2 IX1 SP2 9EDB ee ff SP1 9EEB IMM A4 ii DIR B4 dd EXT IX2 IX1 SP2 9ED4 ee ff SP1 9EE4 ff DIR 38 dd INH 48 INH 58 IX1 SP1 9E68 ff DIR 37 dd INH 47 INH 57 IX1 SP1 9E67 Freescale Semiconductor ...

Page 115

... BNE rel Branch if Not Equal BPL rel Branch if Plus BRA rel Branch Always MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) Description ← 0 – – – – – – – – – – – – ...

Page 116

... INH 4F INH 5F INH 8C IX1 SP1 9E6F ff IMM A1 ii DIR B1 dd EXT IX2 ↕ ↕ ↕ IX1 SP2 9ED1 ee ff SP1 9EE1 ff DIR 33 dd INH 43 INH 53 ↕ ↕ 1 IX1 SP1 9E63 ff EXT IMM ↕ ↕ ↕ DIR 75 dd SP1 9EF3 ff Freescale Semiconductor ...

Page 117

... LDHX #opr16i LDHX opr8a LDHX opr16a Load Index Register (H:X) LDHX ,X from Memory LDHX oprx16,X LDHX oprx8,X LDHX oprx8,SP MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Description (X) – (M) ↕ – – (CCR Updated But Operands Not Changed) U – – (A) ...

Page 118

... INH 62 1 IMM DIR EXT IX2 ↕ ↕ – IX1 SP2 9EDA SP1 9EEA ff 4 INH 87 2 INH 8B 2 INH 89 2 INH 86 3 INH 8A 3 INH 88 3 DIR INH 49 1 INH 59 1 ↕ ↕ ↕ IX1 SP1 9E69 ff 6 Freescale Semiconductor ...

Page 119

... SUB opr16a SUB oprx16,X Subtract SUB oprx8,X SUB ,X SUB oprx16,SP SUB oprx8,SP SWI Software Interrupt MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 8 Central Processor Unit (S08CPUV2) Description ↕ C – – ← 0xFF – – – – – – ...

Page 120

... SP ← (H:X) – 0x0001 – – – – – – I bit ← 0; Halt CPU – – 0 – – – INH 97 1 INH 85 1 DIR INH 4D 1 INH 5D 1 – IX1 SP1 9E6D ff 5 INH 95 2 INH 9F 1 INH 94 2 INH 8F 2+ Freescale Semiconductor ...

Page 121

... Direct IX1 Indexed, 8-Bit Offset EXT Extended IX2 Indexed, 16-Bit Offset DD DIR to DIR IMD IMM to DIR IX+D IX+ to DIR DIX+ DIR to IX+ MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 8-3. Opcode Map (Sheet Read-Modify-Write Control NEGX NEG NEG ...

Page 122

... IX 4 IX2 3 IX1 4 SP2 3 9EDF 5 9EEF STX 4 SP2 3 Prebyte (9E) and Opcode in 9E60 6 HCS08 Cycles Hexadecimal NEG Instruction Mnemonic Addressing Mode Number of Bytes 3 SP1 Freescale Semiconductor 4 SUB SP1 4 CMP SP1 4 SBC SP1 4 9EF3 6 CPX CPHX SP1 3 SP1 4 AND SP1 4 BIT SP1 4 LDA ...

Page 123

... These configurations are summarized in Table 9-1. Configuration Options by Package Type Package Type No. of Backplanes 64-pin 80-pin Figure 9-1 shows the MC9S08LC60 Series block diagram with the LCD highlighted. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor No. of Frontplanes ...

Page 124

... PTC6/BKGD/ output only pin 8. FP[39:32], PTA[1:0], and PTA[7:4] are not available in the 64 LQFP. 9. ACMPO is not available. PTA[7:4]/KBI1P[7:4]/ADP[7:4] PTA3/KBI1P3/ADP3/ACMP– PTA2/KBI1P2/ADP2/ACMP+ PTA[1:0]/KBI1P[1:0]/ADP[1:0] PTB7/KBI2P4/SS1 PTB6/KBI2P3/SPSCK1 PTB5/MOSI1/SCL PTB4/MISO1/SDA PTB3/KBI2P2 PTB2/RESET PTB1/KBI2P1/XTAL PTB0/KBI2P0/EXTAL PTC7/KBI2P7/IRQ/TPMCLK PTC6/BKGD/MS PTC5/KBI2P6/TPM2CH1 PTC4/KBI2P5/TPM2CH0 PTC3/SS2/TPM1CH1 PTC2/SPSCK2/TPM1CH0 PTC1/MOSI2/TxD PTC0/MISO2/RxD Freescale Semiconductor ...

Page 125

... Stop1 all LCD operation is suspended recommended to blank the display before entering stop1 Stop2 all LCD operation is suspended recommended to blank the display before entering stop2. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor (1 and V to monitor their magnitudes.This feature ...

Page 126

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 126 Table 9-2. Modes of Operation (continued) Operation lcd_regs lcd_control lcd_clkgen CONTROL CLOCK INPUT LCD CHARGE PUMP Figure 9-2. LCD Driver Block Diagram LCD RAM FP/BP DRIVER lcd_vgen BASE CLOCK V LL1 V LL2 V LL3 Freescale Semiconductor LCD ...

Page 127

... LL2 LL3 the internal charge pump when it is enabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 9-3. Signal Properties Function Backplane waveform signals that connect directly to the pads High impedance Frontplane waveform signals that connect directly to the pads High impedance ...

Page 128

... DUTY0 and DUTY1. 6 LCD Waveform — The LPWAVE bit allows selection of two types of LCD waveforms. LPWAVE 0 Normal waveforms selected. 1 Low-power waveforms selected. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 128 LCLK2 LCLK1 LCLK0 Table 9-4. LCDCR0 Field Descriptions Description DUTY1 DUTY0 Freescale Semiconductor ...

Page 129

... Allows the LCD module driver and charge pump to continue running during stop3. 1 Disables the LCD module driver and charge pump whenever the MCU goes into stop3. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) Description Equation 9-1 ...

Page 130

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 130 FP6EN FP5EN FP4EN FP13EN FP12EN FP21EN FP20EN FP29EN FP28EN FP37EN FP36EN Description FP3EN FP2EN FP1EN FP11EN FP10EN FP9EN FP19EN FP18EN FP17EN FP27EN FP26EN FP25EN FP35EN FP34EN FP33EN Freescale Semiconductor 0 FP0EN 0 FP8EN 0 FP16EN 0 FP24EN 0 FP32EN 0 FP40EN 0 ...

Page 131

... FP13BP2 W Reset FP15BP3 FP15BP2 W Reset FP17BP3 FP17BP2 W Reset FP19BP3 FP19BP2 W Reset FP21BP3 FP21BP2 W Reset Value is indeterminate MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor FP1BP1 FP1BP0 FP0BP3 FP3BP1 FP3BP0 FP2BP3 FP5BP1 FP5BP0 FP4BP3 FP7BP1 FP7BP0 FP6BP3 FP9BP1 FP9BP0 FP8BP3 FP11BP1 ...

Page 132

... FP35BP0 FP34BP3 FP37BP1 FP37BP0 FP36BP3 FP39BP1 FP39BP0 FP38BP3 FP40BP3 FP22BP2 FP22BP1 FP22BP0 FP24BP2 FP24BP1 FP24BP0 FP26BP2 FP26BP1 FP26BP0 FP28BP2 FP28BP1 FP28BP0 FP30BP2 FP30BP1 FP30BP0 FP32BP2 FP32BP1 FP32BP0 FP34BP2 FP34BP1 FP34BP0 FP36BP2 FP36BP1 FP36BP0 FP38BP2 FP38BP1 FP38BP0 FP40BP2 FP40BP1 FP40BP0 Freescale Semiconductor ...

Page 133

... Figure 9-6. LCD Clock Source Register (LCDCLKS) Read: anytime Write: anytime.It is recommended that CLKADJ[5:0], DIV16, and SOURCE not be modified while the LCDEN bit is asserted. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) Description Description 5 ...

Page 134

... Selects voltage doubler. 1 Selects voltage tripler. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 134 Table 9-9. LCDCLKS Field Descriptions Description DIV16 LCD clock source / ( CPCADJ1 CPCADJ0 HDRVBUF 1 1 Table 9-10. LCDSUPPLY Field Descriptions Description × ) (CLKADJ[5:0] + BBYPASS VSUPPLY1 Freescale Semiconductor Eqn. 9-2 0 VSUPPLY0 1 ...

Page 135

... Figure 9-8. LCD Blink Control Register (LCDBCTL) Read: anytime Write: anytime recommended that BRATE[1:0] and BLKMODE, must not be modified while BLINK is asserted. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) Description × = LCDCLK / (6 ...

Page 136

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 136 Table 9-11. LCDBCTL Field Descriptions Description LCD blink rate calculation (see LCD LCD waveform base clock = (5+ BRATE[2:0 LCDDRMS Table 9-12. LCDCMD Field Descriptions Description Equation 9-4). blink rate calculation. Eqn. 9 BLANK LCDCLR 0 0 Freescale Semiconductor 0 0 ...

Page 137

... For a detailed description of LCD module operation for a basic seven-segment LCD display, see Seven Segment Example Description”. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 9-12. LCDCMD Field Descriptions Description Chapter 9 Liquid Crystal Display Driver (S08LCDV1) Section 9.6.1, “LCD ...

Page 138

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 138 Table 9-13. LCD Module Duty Cycle Modes LCDCR0 Register DUTY1 DUTY0 BP3 0 1 OFF 1 0 OFF 1 1 BP3 0 0 N/A Backplanes BP2 BP1 BP0 OFF BP1 BP0 BP2 BP1 BP0 BP2 BP1 BP0 N/A N/A N/A Freescale Semiconductor ...

Page 139

... LCDCLK using different values of DIV16 and CLKADJ[5:0] for a range of clock inputs frequencies. Using an external 32.768-kHz clock input is required for reduced power consumption applications. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1 (voltage level – 1) Frame Frequency ...

Page 140

... Freescale Semiconductor 20000 1250 625 416.7 312.5 250.0 208.3 178.6 156.3 138.9 125.0 113.6 104.2 96.2 89.3 83.3 78.1 73.5 69.4 65 ...

Page 141

... This section shows the timing examples of the LCD output waveforms for the available modes of operation. As shown in Table 9-16, all examples use 1/3 bias mode. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) LCD Base Frequency ) (Hz) 2049 ...

Page 142

... Chapter 9 Liquid Crystal Display Driver (S08LCDV1) Table 9-16. Configurations for Example LCD Waveforms Example 1 Example 2 Example 3 Example 4 Example 5 Example 6 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 142 Bias Mode DUTY[1:0] Duty Cycle 01 1/2 01 1/2 10 1/3 1/3 10 1/3 11 1/4 11 1/4 LPWAVE bit Freescale Semiconductor ...

Page 143

... BP0 BP1 FPx (xx10) BP0-FPx (OFF) BP1-FPx (ON) Figure 9-11. 1/2 Duty and 1/3 Bias (Normal Waveform) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) VLCD VLCD × 2/3 VLCD × 1/3 VSSX VLCD VLCD × 2/3 VLCD × ...

Page 144

... VLCD × 1/3 VSSX VLCD VLCD × 2/3 VLCD × 1/3 VSSX +VLCD +VLCD × 2/3 +VLCD × 1/3 0 -VLCD × 1/3 -VLCD × 2/3 -VLCD +VLCD +VLCD × 2/3 +VLCD × 1/3 0 -VLCD × 1/3 -VLCD × 2/3 -VLCD Freescale Semiconductor ...

Page 145

... BP1 BP2 FPx (x010) BP0-FPx (OFF) BP1-FPx (ON) Figure 9-13. 1/3 Duty and 1/3 Bias (Normal Waveform) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) VLCD VLCD × 2/3 VLCD × 1/3 VSSX VLCD VLCD × 2/3 VLCD × ...

Page 146

... VLCD × 1/3 VSSX VLCD VLCD × 2/3 VLCD × 1/3 VSSX +VLCD +VLCD × 2/3 +VLCD × 1/3 0 -VLCD × 1/3 -VLCD × 2/3 -VLCD +VLCD +VLCD × 2/3 +VLCD × 1/3 0 -VLCD × 1/3 -VLCD × 2/3 -VLCD Freescale Semiconductor ...

Page 147

... BP2 BP3 FPx (1001) BP0-FPx (ON) BP1-FPx (OFF) Figure 9-15. 1/4 Duty and 1/3 Bias (Normal Waveform) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) 1 Frame VLCD VLCD × 2/3 VLCD × 1/3 VSSX VLCD VLCD × ...

Page 148

... VLCD × 1/3 VSSX VLCD VLCD × 2/3 VLCD × 1/3 VSSX +VLCD +VLCD × 2/3 +VLCD × 1/3 0 -VLCD × 1/3 -VLCD × 2/3 -VLCD +VLCD +VLCD × 2/3 +VLCD × 1/3 0 -VLCD × 1/3 -VLCD × 2/3 -VLCD Freescale Semiconductor ...

Page 149

... When the BLINK bit is modified to start or stop the LCD display blinking, the BLINK command change takes place at the beginning of the next LCD frame cycle. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 9 Liquid Crystal Display Driver (S08LCDV1) If LCDDRMS = 1, the LCDRAM register bank ...

Page 150

... BRATE[2:0]) 512 1024 2048 4096 voltage divider. LCD illustrates several potential Freescale Semiconductor ...

Page 151

... V is recommended that a low equivalent series resistance (ESR) capacitor be used. Proper orientation is imperative when using a polarized capacitor. The recommended value for the external capacitor is 0.1 μF. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor LCDCPMS R1 ~(LCDCPMS (~(LCDCPMS) & ...

Page 152

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 152 This LCD module configurability makes the LCD module LCD. are will be generated internally. LL3 , V , and V LL1 LL2 must be provided by external hardware. Figure 9-17, LCDCPMS bit are not generated internally. LL3 Freescale Semiconductor ...

Page 153

... V). The figure above shows that V The voltage divider block uses the states of LCDCPMS, BBYPASS, and powersw3 to derive a state for V . LL1 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor or it can be externally derived from a voltage DD Table 9-18. V Switch Option DD LCD Power Supply Configuration voltage to V level ...

Page 154

... LCD LCD Operation). Table 9-19 shows the . LCDCPMS = 1 Voltage Tripler = 3 × LL1 ref LL3 ref 1.4 V 4.2 V 1.5 V 4.5 V 1.67 V 5.0 V 1.8 V 5.4 V should be LL3 will be configured LCD LL1, LL2, LL3 , the charge pump DD Freescale Semiconductor ref. ...

Page 155

... Initialization Section This section provides a recommended initialization sequence for the LCD module and also includes initialization examples for several possible LCD application scenarios. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 9-20. V Switch Option DD Recommend Use for 3-V ...

Page 156

... Configure the blink mode to blink individual or blink all segments (BLKMODE bit) b) Configure the blink frequency (BRATE[2:0]) 6. FPENR[5:0] register a) Enable the LCD module frontplane waveform output (FP[40:0]EN bits) 7. LCDCR0 register a) Enable the LCD module (LCDEN bit) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 156 Freescale Semiconductor ...

Page 157

... LCD glass operating voltage • LCD segment count • varied blink modes/frequencies • LCD frame rate MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor lists each example and the setup requirements. Table 9-21. LCD Application Scenarios LCD Glass Required LCD Operating LCD ...

Page 158

... For 128 segments (4x32), select 1/4 duty cycle (see table 9-11) X N/A; Blink Segments = 0; Blink All = 1 N/A Only 32 Frontplanes need to be enabled. Behavior in Blinking LCD Power STOP3 and Mode/Rate Input WAIT modes No Blinking WAIT: on Power via STOP3 Comment LCD should be 1.5-V. LCD Freescale Semiconductor LCD (see ...

Page 159

... LCDCPMS HDRVBUF CPCADJ[1:0] BBYPASS VSUPPLY[1:0] LCDCR1 LCDWAI XXXXXX01 LCDSTP3 LCDCR0 LCLK[2:0] 0X011X11 LPWAVE DUTY[1:0] MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Example 2 LCD Glass Required LCD Operating LCD Frame Voltage segments Rate 3 Individual segment 1 Selects the bus clock as the LCD clock input External clock reference = 0 ...

Page 160

... Using the LCD base frequency for the selected LCD frame frequency, select 0.5 Hz blink frequency (see table 9-15). Only 33 Frontplanes need to be enabled. Optionally, if required, 1/4 duty cycle could be used. This option would only require 25 frontplane pins to be enabled. Comment Freescale Semiconductor ...

Page 161

... BRATE[2:0] FPENR[5:0] FPENR0 11111111 FPENR1 11111111 FPENR2 11111111 FPENR3 11111111 FPENR4 11111111 FPENR5 XXXXXXX0 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Example 3 LCD Glass Required LCD Operating LCD Frame Voltage segments Rate 5-V 160 60 Hz Individual segment 1 Selects the bus clock as the LCD clock input External clock reference = 0 ...

Page 162

... Using the LCD base frequency for the selected LCD frame frequency, select 2.0 Hz blink frequency (see table 9-15). All 41 LCD frontplanes need to be enabled. Behavior in LCD Blinking STOP3 and Power Mode/Rate WAIT modes Input all segment WAIT: off Power 2.0 Hz STOP3: off via V LCD Comment LCD should be 1.67-V. LCD Freescale Semiconductor (see ...

Page 163

... BP1, BP2) and frontplace pins (FP0, FP1, and FP2). LCDRAM contents and output waveforms are also shown. Output waveforms are illustrated in Figure 9-20. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor LCD Segment Energize Blink Enable and Command LCDRAM Mode Select ...

Page 164

... Figure 9-19. Waveform Output from LCDRAM Registers MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 164 BP CONNECTION a BP0 (a, b COMMONED BP1 ( COMMONED BP2 (d, e COMMONED) F1B0 F0B3 F0B2 F0B1 F0B0 a — — FP0 F3B0 F2B3 F2B2 F2B1 F2B0 — — — FP2 Freescale Semiconductor ...

Page 165

... DUTY = 1/3 F0B2 F0B1 F0B0 — F1B2 F1B1 F1B0 — F2B2 F2B1 F2B0 — MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 1FRAME BP0 BP1 BP2 FP0 FP1 FP2 Figure 9-20. LCD Waveforms (LPWAVE = 0) Chapter 9 Liquid Crystal Display Driver (S08LCDV1 ...

Page 166

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 166 Figure 9-21. “f” Segment Voltage Waveform therefore the segment will –V 1 –V 2 –V 3 threshold therefore the –V 1 –V 2 –V 3 Figure 9-23 shows two Freescale Semiconductor ...

Page 167

... Doubler Buffered Mode V LCD Note: Current consumption data based on using the external 32-kHz oscillator with LCD configured using the low-power wave forms option, a 1/4 duty, and a 32-Hz frame frequency. C MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor FP[40:0] BP[3:0] 9S08LC60 V LCD ...

Page 168

... Chapter 9 Liquid Crystal Display Driver (S08LCDV1) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 168 Freescale Semiconductor ...

Page 169

... ICGLCLK is the alternate BDC clock source for the MC9S08LC60 Series. Figure 10-1. System Clock Distribution Diagram Freescale Semiconductor programs a factory trim value for ICGTRM into the FLASH location $FFBE (NVICGTRM). Leaving this address for the ICGTRM value also allows debugger and programmer vendors to perform a manual trim operation and store the resultant ICGTRM value into NVICGTRM for users to access at a later time ...

Page 170

... FP[39:32], PTA[1:0], and PTA[7:4] are not available in the 64 LQFP. 9. ACMPO is not available. PTA[7:4]/KBI1P[7:4]/ADP[7:4] PTA3/KBI1P3/ADP3/ACMP– PTA2/KBI1P2/ADP2/ACMP+ PTA[1:0]/KBI1P[1:0]/ADP[1:0] PTB7/KBI2P4/SS1 PTB6/KBI2P3/SPSCK1 PTB5/MOSI1/SCL PTB4/MISO1/SDA PTB3/KBI2P2 PTB2/RESET PTB1/KBI2P1/XTAL PTB0/KBI2P0/EXTAL PTC7/KBI2P7/IRQ/TPMCLK PTC6/BKGD/MS PTC5/KBI2P6/TPM2CH1 PTC4/KBI2P5/TPM2CH0 PTC3/SS2/TPM1CH1 PTC2/SPSCK2/TPM1CH0 PTC1/MOSI2/TxD PTC0/MISO2/RxD . IRQ should not be driven above Freescale Semiconductor ...

Page 171

... Uses external or internal clock as reference frequency • Automatic lockout of non-running clock sources • Reset or interrupt on loss of clock or loss of FLL lock MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 10 Internal Clock Generator (S08ICGV4) Figure 10-3, the ICG consists Section 10.6, “Initialization/Application 171 ...

Page 172

... The FLL DCO frequency is off target and the FLL is adjusting the DCO to match the target frequency. — FLL engaged external locked is a state which occurs when the FLL detects that the DCO is locked to a multiple of the internal reference. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 172 Freescale Semiconductor ...

Page 173

... If upon the first write to ICGC1, either the FEE mode or FBE mode is selected, this pin functions as the output of the oscillator circuit. If upon the first write to ICGC1, either the FEI mode or SCM mode is MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor ICG SELECT ...

Page 174

... Recommended component values are listed in the Figure 10-5. External Frequency Reference Connection MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 174 ICG EXTAL V SS CLOCK INPUT Figure 10-4. External Clock Connections ICG EXTAL CRYSTAL OR RESONATOR Figure 10-4. XTAL NOT CONNECTED Electrical Characteristics chapter. XTAL R S Freescale Semiconductor ...

Page 175

... The CLKS bits are writable at any time, unless the first write after a reset was CLKS = 0X, the CLKS bits cannot be written to 1X until after the next reset (because the EXTAL pin was not reserved). MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Memory chapter of this data sheet for the absolute address ...

Page 176

... Oscillator disabled when ICG is in off mode unless ENABLE is high, CLKS = 10, and REFST = 1. 1 Oscillator enabled when ICG is in off mode, CLKS = 1X and REFST = 1. 1 Loss of Clock Disable LOCD 0 Loss of clock detection enabled. 1 Loss of clock detection disabled. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 176 Description Freescale Semiconductor ...

Page 177

... Division factor = 2 010 Division factor = 4 011 Division factor = 8 100 Division factor = 16 101 Division factor = 32 110 Division factor = 64 111 Division factor = 128 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor 5 4 MFD LOCRE 0 0 Figure 10-7. ICG Control Register 2 (ICGC2) ...

Page 178

... Writing a logic 0 to ICGIF has no effect ICG interrupt request is pending ICG interrupt request is pending. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 178 REFST LOLS LOCK Figure 10-8. ICG Status Register 1 (ICGS1) Description LOCS ERCS ICGIF Freescale Semiconductor ...

Page 179

... CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor ...

Page 180

... FLL, configure the ICG so that the frequency of ICGDCLK does not exceed its maximum value to ensure proper MCU operation. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 180 FLT Description TRIM Figure 10-12. ICG Trim Register (ICGTRM) Description Freescale Semiconductor ...

Page 181

... ICGOUT will double if the FLL was unlocked. ICGDCLK If this mode is entered from off mode, f MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 10 Internal Clock Generator (S08ICGV4) will default to f ICGDCLK Self_reset will maintain the previous frequency.If this mode ...

Page 182

... CLOCK SELECT CIRCUIT FLT DIGITAL DIGITALLY CONTROLLED LOOP OSCILLATOR FILTER FLL ANALOG CLKST PULSE COUNTER RESET AND INTERRUPT CONTROL LOCS ERCS LOCD ICGIF LOLRE RFD REDUCED ICGOUT FREQUENCY DIVIDER (R) ICGDCLK 1x 2x FREQUENCY- LOCKED LOOP (FLL) ICG2DCLK IRQ RESET LOCRE Freescale Semiconductor ...

Page 183

... MHz in FEE mode to prevent over-clocking the DCO. The minimum multiplier for the FLL, from operational limit of the DCO, the reference clock cannot be any faster than 10 MHz. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor or less than the minimum n unlock (max) and greater than n ...

Page 184

... If Δn goes outside this range unlock or less than lock / (2×R) This ICGDCLK (max) and greater lock /R. In FLL engaged external ICGDCLK (max). After the FLL has locked, Δn Freescale Semiconductor ...

Page 185

... If ENABLE is high (waiting for external crystal start-up after exiting stop). 2 DCO clock will not be monitored until DCOS = 1 upon entering SCM from off or FLL bypassed external mode. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor and f , respectively, the LOCS status bit will be set to indicate LOR ...

Page 186

... SCM ICGDCLK/R — ICGDCLK/R — DCOS = 0 or ICGDCLK/R — ICGDCLK/R DCOS = 1 ICGDCLK/R — ERCS = 1 — ERCS = 1 and 3 DCOS = 1 ERCS = 1 and (2) DCOS = 1 Freescale Semiconductor Reason CLKS1 ≠ CLKST — ERCS = 0 — DCOS = 0 ERCS = 0 ERCS = 0 — ERCS = 0 — LOCS = 1 & ERCS = 1 — — ...

Page 187

... For other applications, lowest power consumption may be the chief clock consideration. Still others may have lowest cost as the primary goal. The ICG allows great flexibility in choosing which is best for any application. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 10 Internal Clock Generator (S08ICGV4) Table 10-11), N and R are determined by Table 10-12) ...

Page 188

... Clock Reference Source = External < 20 MHz Bus range ≤ 8 MHz when crystal or resonator is P Note NA Typical f ICGOUT immediately after reset NA 64 Typical f = 243 kHz IRG . ICGDCLKmax Division Factor (R) ÷1 ÷2 ÷4 ÷8 ÷16 Freescale Semiconductor = 8 MHz ...

Page 189

... This is read only; should read DCOS = 1 before performing any time critical tasks ICGFLTLU/L = $xx Only needed in self-clocked mode; FLT will be adjusted by loop to give 8.38 MHz DCO clock Bits 15:12 unused 0000 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Table 10-12. MFD and RFD Decode Table 101 110 111 = ...

Page 190

... RECOVERY FROM STOP OSCSTEN = 1 CHECK NO FLL LOCK STATUS. LOCK = 1? YES CONTINUE NOTE: THIS WILL REQUIRE THE OSCILLATOR TO START AND STABILIZE. ACTUAL TIME IS DEPENDENT ON CRYSTAL /RESONATOR AND EXTERNAL CIRCUITRY. RECOVERY FROM STOP OSCSTEN = 0 CHECK NO FLL LOCK STATUS. LOCK = 1? YES CONTINUE Freescale Semiconductor ...

Page 191

... ICGS2 = $xx This is read only. Should read DCOS before performing any time critical tasks ICGFLTLU/L = $xx Not used in this example ICGTRM Not used in this example MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor = 4.00 MHz ext ext Configures oscillator for low power Configures oscillator for high-frequency range ...

Page 192

... Figure 10-15. ICG Initialization and Stop Recovery for Example #2 MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 192 RECOVERY RESET FROM STOP INITIALIZE ICG SERVICE INTERRUPT ICGC1 = $7A ICGC2 = $30 SOURCE (f CHECK NO LOCK = 1? FLL LOCK STATUS LOCK = 1? YES CONTINUE CONTINUE = 4 MHz) Bus CHECK NO YES Freescale Semiconductor ...

Page 193

... ICGS2 = $xx This is read only; good idea to read this before performing time critical operations ICGFLTLU/L = $xx Not used in this example MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor / 64, f IRG IRG Configures oscillator for low power Configures oscillator for low-frequency range; FLL prescale factor is 64 Oscillator using crystal or resonator requested (bit is really a don’ ...

Page 194

... MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 194 Only need to write when trimming internal oscillator; done in separate operation (see example #4) NO YES NOTE: THIS WILL REQUIRE THE INTERAL REFERENCE CLOCK TO START AND STABILIZE. RECOVERY FROM STOP CHECK NO FLL LOCK STATUS. LOCK = 1? YES CONTINUE Freescale Semiconductor ...

Page 195

... If the intended bus frequency is near the maximum allowed for the device recommended to trim using a reduction divisor (R) twice the final value. After the trim procedure is complete, the reduction divisor can be restored. This will prevent accidental overshoot of the maximum clock frequency. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor START TRIM PROCEDURE ICGTRM = $80 MEASURE ...

Page 196

... Chapter 10 Internal Clock Generator (S08ICGV4) MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 196 Freescale Semiconductor ...

Page 197

... I/O port pins (refer to the The MC9S08LC60 Series has two TPM modules Figure 11-1 shows the MC9S08LC60 Series block diagram with the TPMs highlighted. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Pins and Connections chapter for more information). 197 ...

Page 198

... FP[39:32], PTA[1:0], and PTA[7:4] are not available in the 64 LQFP. 9. ACMPO is not available. PTA[7:4]/KBI1P[7:4]/ADP[7:4] PTA3/KBI1P3/ADP3/ACMP– PTA2/KBI1P2/ADP2/ACMP+ PTA[1:0]/KBI1P[1:0]/ADP[1:0] PTB7/KBI2P4/SS1 PTB6/KBI2P3/SPSCK1 PTB5/MOSI1/SCL PTB4/MISO1/SDA PTB3/KBI2P2 PTB2/RESET PTB1/KBI2P1/XTAL PTB0/KBI2P0/EXTAL PTC7/KBI2P7/IRQ/TPMCLK PTC6/BKGD/MS PTC5/KBI2P6/TPM2CH1 PTC4/KBI2P5/TPM2CH0 PTC3/SS2/TPM1CH1 PTC2/SPSCK2/TPM1CH0 PTC1/MOSI2/TxD PTC0/MISO2/RxD . IRQ should not be driven above Freescale Semiconductor ...

Page 199

... Set, clear, or toggle output compare action — Selectable polarity on PWM outputs 11.1.2 Block Diagram Figure 11-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels. MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4 Freescale Semiconductor Chapter 11 Timer/Pulse-Width Modulator (S08TPMV2) 199 ...

Page 200

... ELS1B ELS1A CH1F CH1IE MS1B MS1A ELSnB ELSnA CHnF CHnIE MSnA MSnB Figure 11-2. TPM Block Diagram DIVIDE BY PS1 PS0 TOF INTERRUPT LOGIC TOIE PORT TPMxCH0 LOGIC INTERRUPT LOGIC TPMxCH1 PORT LOGIC INTERRUPT LOGIC TPMxCHn PORT LOGIC INTERRUPT LOGIC Freescale Semiconductor ...