C8051F34B-GQ Silicon Laboratories Inc, C8051F34B-GQ Datasheet - Page 192

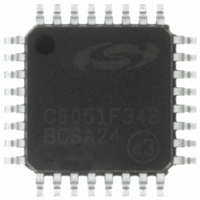

C8051F34B-GQ

Manufacturer Part Number

C8051F34B-GQ

Description

IC 8051 MCU 32K FLASH 32LQFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F34xr

Datasheet

1.C8051F349-GQ.pdf

(276 pages)

Specifications of C8051F34B-GQ

Program Memory Type

FLASH

Program Memory Size

32KB (32K x 8)

Package / Case

32-LQFP

Core Processor

8051

Core Size

8-Bit

Speed

48MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART, USB

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 17x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

I2C/SMBus/SPI/UART/USB

Maximum Clock Frequency

48 MHz

Number Of Programmable I/os

25

Number Of Timers

4

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

KSK-SL-F34X, KSK-SL-TOOLSTICK, PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F340DK

Minimum Operating Temperature

- 40 C

Package

32LQFP

Device Core

8051

Family Name

C8051F34x

Maximum Speed

48 MHz

Operating Supply Voltage

3.3|5 V

On-chip Adc

17-chx10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1748 - ADAPTER TOOLSTICK FOR C8051F34X

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1534

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F34B-GQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Company:

Part Number:

C8051F34B-GQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

- Current page: 192 of 276

- Download datasheet (2Mb)

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

SMBus configuration options include:

•

•

•

•

These options are selected in the SMB0CF register, as described in

tion Register” on page 192

17.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes,

select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is

set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the

INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however,

the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit

is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of

the current transfer).

The SMBCS1-0 bits select the SMBus clock source, which is used only when operating as a master or

when the Free Timeout detection is enabled. When operating as a master, overflows from the selected

source determine the absolute minimum SCL low and high times as defined in Equation 17.1. Note that the

selected clock source may be shared by other peripherals so long as the timer is left running at all times.

For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer

configuration is covered in

The selected clock source should be configured to establish the minimum SCL High and Low times as per

Equation 17.1. When the interface is operating as a master (and SCL is not driven or extended by any

other devices on the bus), the typical SMBus bit rate is approximated by Equation 17.2.

192

Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

SDA setup and hold time extensions

Slave event enable/disable

Clock source selection

SMBCS1

Equation 17.1. Minimum SCL High and Low Times

0

0

1

1

Table 17.1. SMBus Clock Source Selection

Section “21. Timers” on page 235

T

Equation 17.2. Typical SMBus Bit Rate

.

HighMin

SMBCS0

BitRate

=

0

1

0

1

T

LowMin

=

f

--------------------------------------------- -

ClockSourceOverflow

Rev. 1.3

=

Timer 2 High Byte Overflow

Timer 2 Low Byte Overflow

--------------------------------------------- -

f

ClockSourceOverflow

SMBus Clock Source

3

Timer 0 Overflow

Timer 1 Overflow

.

1

Section “17.4.1. SMBus Configura-

Related parts for C8051F34B-GQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc