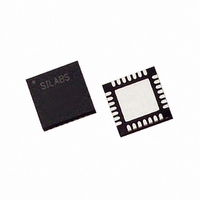

C8051F315-GMR Silicon Laboratories Inc, C8051F315-GMR Datasheet - Page 161

C8051F315-GMR

Manufacturer Part Number

C8051F315-GMR

Description

IC 8051 MCU 8K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F31xr

Specifications of C8051F315-GMR

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

25

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

- Current page: 161 of 228

- Download datasheet (2Mb)

14.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the table below, STATUS

VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. Note that the

shown response options are only the typical responses; application-specific procedures are allowed as

long as they conform to the SMBus specification. Highlighted responses are allowed but do not conform to

the SMBus specification.

1100

1000

1110

Values Read

0

0

0

1

0

0

0

0

X

X

0

1

Current SMbus State

A master START was

generated.

A master data or address byte

was transmitted; NACK

received.

A master data or address byte

was transmitted; ACK

received.

A master data byte was

received; ACK requested.

Table 14.4. SMBus Status Decoding

Rev. 1.7

C8051F310/1/2/3/4/5/6/7

Typical Response Options

Load slave address + R/W into

SMB0DAT.

Set STA to restart transfer.

Abort transfer.

Load next data byte into

SMB0DAT.

End transfer with STOP.

End transfer with STOP and start

another transfer.

Send repeated START.

Switch to Master Receiver Mode

(clear SI without writing new data

to SMB0DAT).

Acknowledge received byte; Read

SMB0DAT.

Send NACK to indicate last byte,

and send STOP.

Send NACK to indicate last byte,

and send STOP followed by

START.

Send ACK followed by repeated

START.

Send NACK to indicate last byte,

and send repeated START.

Send ACK and switch to Master

Transmitter Mode (write to

SMB0DAT before clearing SI).

Send NACK and switch to Master

Transmitter Mode (write to

SMB0DAT before clearing SI).

0

1

0

0

0

1

1

0

0

0

1

1

1

0

0

Written

Values

0

0

1

0

1

1

0

0

0

1

1

0

0

0

0

161

X

X

X

X

X

X

X

X

1

0

0

1

0

1

0

Related parts for C8051F315-GMR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc