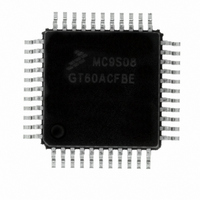

MC9S08GT60ACFBE Freescale Semiconductor, MC9S08GT60ACFBE Datasheet - Page 160

MC9S08GT60ACFBE

Manufacturer Part Number

MC9S08GT60ACFBE

Description

IC MCU 60K FLASH 4K RAM 44-QFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Datasheet

1.MC9S08GT60ACFDER.pdf

(302 pages)

Specifications of MC9S08GT60ACFBE

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

36

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-QFP

Cpu Family

HCS08

Device Core Size

8b

Frequency (max)

40MHz

Interface Type

I2C/SCI/SPI

Total Internal Ram Size

4KB

# I/os (max)

36

Number Of Timers - General Purpose

4

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Operating Supply Voltage (min)

1.8/2.08V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

44

Package Type

PQFP

Processor Series

S08GT

Core

HCS08

Data Bus Width

8 bit

Data Ram Size

4 KB

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

39

Number Of Timers

2

Operating Supply Voltage

0 V to 1.8 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWS08

Development Tools By Supplier

M68EVB908GB60E, M68DEMO908GB60E

Minimum Operating Temperature

- 40 C

For Use With

M68DEMO908GB60E - BOARD DEMO MC9S08GB60M68EVB908GB60E - BOARD EVAL FOR MC9S08GB60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08GT60ACFBE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC9S08GT60ACFBE

Manufacturer:

FREESCALE深圳进口

Quantity:

20 000

Company:

Part Number:

MC9S08GT60ACFBER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Timer/PWM (TPM)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter

for read operations. Whenever either byte of the counter is read (TPMxCNTH or TPMxCNTL), both bytes

are captured into a buffer so when the other byte is read, the value will represent the other byte of the count

at the time the first byte was read. The counter continues to count normally, but no new value can be read

from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer

count TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency

mechanism in case only one byte of the counter was read before resetting the count.

10.5.2

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits

in the channel n status and control registers determine the basic mode of operation for the corresponding

channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

10.5.2.1

With the input capture function, the TPM can capture the time at which an external event occurs. When an

active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter

into the channel value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may

be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support

coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to

the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

10.5.2.2

With the output compare function, the TPM can generate timed pulses with programmable position,

polarity, duration, and frequency. When the counter reaches the value in the channel value registers of an

output compare channel, the TPM can set, clear, or toggle the channel pin.

In output compare mode, values are transferred to the corresponding timer channel value registers only

after both 8-bit bytes of a 16-bit register have been written. This coherency sequence can be manually reset

by writing to the channel status/control register (TPMxCnSC).

An output compare event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

10.5.2.3

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS = 0) and can

be used when other channels in the same TPM are configured for input capture or output compare

functions. The period of this PWM signal is determined by the setting in the modulus register

(TPMxMODH:TPMxMODL). The duty cycle is determined by the setting in the timer channel value

160

Channel Mode Selection

Input Capture Mode

Output Compare Mode

Edge-Aligned PWM Mode

MC9S08GB60A Data Sheet, Rev. 2

Freescale Semiconductor