AT91RM9200-QI-002 Atmel, AT91RM9200-QI-002 Datasheet - Page 36

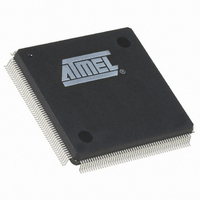

AT91RM9200-QI-002

Manufacturer Part Number

AT91RM9200-QI-002

Description

IC ARM9 MCU 208 PQFP

Manufacturer

Atmel

Series

AT91SAMr

Datasheets

1.AT91RM9200-EK.pdf

(41 pages)

2.AT91RM9200-DK.pdf

(2 pages)

3.AT91RM9200-QU-002.pdf

(701 pages)

Specifications of AT91RM9200-QI-002

Core Processor

ARM9

Core Size

16/32-Bit

Speed

180MHz

Connectivity

EBI/EMI, Ethernet, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

POR

Number Of I /o

122

Program Memory Size

128KB (128K x 8)

Program Memory Type

ROM

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

208-MQFP, 208-PQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT91RM9200-QI-002 SL383

Manufacturer:

Atmel

Quantity:

10 000

13. Revision History

36

Doc. Rev

Lit°1768A

Lit°1768B

Lit°1768C

Lit°1768D

Lit°1768E

Lit°1768F

Doc. Rev

1768GS

Doc. Rev

1768HS

Doc. Rev

1768IS

AT91RM9200

Source

Source

Review

Source

CSRs/Review

CSR 04-066

CSR 03-209

CSR 03-244

CSR 04-315

CSR 03-209

Source

CSR 05-348

Comments

• Date Qualified: May 2001

• Date Qualified: September 2001

• Date Qualified: November 2001

• Date Qualified: 5 Mar-02

• Date Qualified: 12-Jul-02

• Date Qualified: 5 Feb-03

Comments

• Date Qualified: 04-Sep-03

• Page 2; Added Description.

• Page 3; Updated Figure 1, Block Diagram, remove reference to Multi-master Memory Controller.

• Page 4; Added section Key Features. Updated all descriptions of key blocks

• Page 17; Added text to section Peripheral Multiplexing on PIO Lines.

• Page 18; Expanded Table 3, Multiplexing on PIO Controller A.

• Page 19: Expanded Table 4, Multiplexing on PIO Controller B.

• Page 20; Expanded Table 5, Multiplexing on PIO Controller C.

• Page 21; Expanded Table 6, Multiplexing on PIO Controller D.

• Page 27; Updated Table 8, Peripheral Identifiers, Peripheral ID 1 description.

• Page 28; Added section Product Memory Mapping.

• Page 30; Updated and corrected Figure 6, System Peripherals Mapping.

• Page 31; Updated and corrected Figure 7, User Peripherals Mapping.

Comments

• Date Qualified: Unqualified/Internal on Intranet 27-Jan-05

• Global; Reformat in Corporate Template.

• Global; Peripheral Data Controller (PDC) renamed Peripheral DMA Controller.

• Page 1; Features: USART Hardware Handshaking. Software Handshaking removed.

• Page 3; Figure 1: NWAIT pin added to block diagram.

• Page 14; Table 1. AT91RM9200 Pinout for 208-lead PQFP package, pins 28, 30, 37 and 39

names changed

• Page 23; Table 7. Pin Description, ICE and JTAG description, “Internal Pullup” added to

comments for all signals, except TDO.

• Page 24; Table 7. Pin Description, NWAIT pin added.

Comments

Corrected power consumption values on page 1.

In

JTAGSEL, TDI, TCK, TMS, NTRST, TST0, TST1 and NRST.

Table 4-7, “Pin Description List,” on page 24

added mention of Schmitt trigger for pins

1768MS–ATARM–09-Jul-09