EP7312-CR-90 Cirrus Logic Inc, EP7312-CR-90 Datasheet - Page 21

EP7312-CR-90

Manufacturer Part Number

EP7312-CR-90

Description

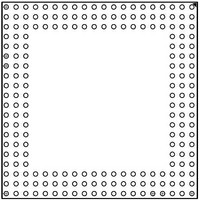

IC ARM720T MCU 90MHZ 204-TFBGA

Manufacturer

Cirrus Logic Inc

Series

EP7r

Datasheet

1.EP7312-CVZ.pdf

(64 pages)

Specifications of EP7312-CR-90

Core Processor

ARM7

Core Size

32-Bit

Speed

90MHz

Connectivity

Codec, DAI, EBI/EMI, IrDA, Keypad, SPI/Microwire1, UART/USART

Peripherals

LCD, LED, MaverickKey, PWM

Number Of I /o

27

Program Memory Type

ROMless

Ram Size

56K x 8

Voltage - Supply (vcc/vdd)

2.3 V ~ 2.7 V

Oscillator Type

External

Operating Temperature

0°C ~ 70°C

Package / Case

204-TFBGA

Processor Series

EP73xx

Core

ARM720T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB7312

For Use With

598-1209 - KIT DEVELOPMENT EP73XX ARM7

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Lead Free Status / Rohs Status

No

Other names

598-1236

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP7312-CR-90

Manufacturer:

CIRRUSLOG

Quantity:

479

Company:

Part Number:

EP7312-CR-90

Manufacturer:

Cirrus Logic Inc

Quantity:

10 000

Static Memory

Figure 7

values for the timings of each of the Static Memory modes.

DS508F1

EXPCLK rising edge to nCS assert delay time

EXPCLK falling edge to nCS deassert hold time

EXPCLK rising edge to A assert delay time

EXPCLK falling edge to A deassert hold time

EXPCLK rising edge to nMWE assert delay time

EXPCLK rising edge to nMWE deassert hold time

EXPCLK falling edge to nMOE assert delay time

EXPCLK falling edge to nMOE deassert hold time

EXPCLK falling edge to HALFWORD deassert delay time

EXPCLK falling edge to WORD assert delay time

EXPCLK rising edge to data valid delay time

EXPCLK falling edge to data invalid delay time

Data setup to EXPCLK falling edge time

EXPCLK falling edge to data hold time

EXPCLK rising edge to WRITE assert delay time

EXPREADY setup to EXPCLK falling edge time

EXPCLK falling edge to EXPREADY hold time

through

Figure 10

define the timings associated with all phases of the Static Memory. The following table contains the

Parameter

©

Copyright Cirrus Logic, Inc. 2005

(All Rights Reserved)

Symbol

t

t

t

t

t

t

t

MOEd

MOEh

t

t

t

t

MWd

MWh

t

HWd

WDd

WRd

CSd

CSh

t

t

t

t

Dnv

t

EXs

EXh

Ad

Ah

Dv

Ds

Dh

High-Performance, Low-Power System on Chip

Min

2

2

4

3

3

3

3

2

2

2

8

6

5

-

-

-

-

Typ

10

13

15

11

8

7

9

6

6

7

7

8

8

-

-

-

-

Max

20

20

16

19

10

10

10

10

20

16

21

30

23

1

3

0

0

EP7312

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

21