SX28AC/DP-G Parallax Inc, SX28AC/DP-G Datasheet - Page 39

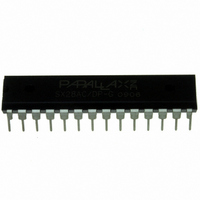

SX28AC/DP-G

Manufacturer Part Number

SX28AC/DP-G

Description

IC MCU 2K FLASH 50MHZ 28DIP

Manufacturer

Parallax Inc

Series

SXr

Datasheet

1.SX20ACSS-G.pdf

(51 pages)

Specifications of SX28AC/DP-G

Core Size

8-Bit

Program Memory Size

3KB (2K x 12)

Oscillator Type

Internal

Core Processor

RISC

Speed

75MHz

Peripherals

Brown-out Detect/Reset, POR, WDT

Number Of I /o

20

Program Memory Type

FLASH

Ram Size

136 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Operating Temperature

0°C ~ 70°C

Package / Case

28-DIP (0.300", 7.62mm)

Controller Family/series

SX

No. Of I/o's

20

Eeprom Memory Size

2048Byte

Ram Memory Size

136Byte

Cpu Speed

75MHz

Processor Series

Ubicom SXx

Core

RISC

Data Bus Width

8 bit

Data Ram Size

136 B

Maximum Clock Frequency

75 MHz

Number Of Programmable I/os

20

Number Of Timers

1

Operating Supply Voltage

4.5 V to 5.5 V

Maximum Operating Temperature

+ 70 C

Mounting Style

Through Hole

Development Tools By Supplier

32300, 28138, 45302

Minimum Operating Temperature

0 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Connectivity

-

Lead Free Status / Rohs Status

Details

Other names

SX28AC/DP

SX28AC/DP

SX28AC/DP

Parallax SX20AC/SX28AC

16.1.

Some

mnemonics that are special cases of existing instructions

or alternative mnemonics for standard ones. For example,

an assembler might support the mnemonic “CLC” (clear

Note 1: The JMP W and JMP PC+W instructions take 4 cycles in the Slow clocking mode, or 3 cycles in the Turbo clocking mode.

Note 2: The SC instruction takes 1 cycle if the tested condition is false or 2 cycles if the tested condition is true.

Note 3: The assembler converts the SKIP instruction into a SNB or SB instruction that tests the least significant bit of the program

counter, choosing SNB or SB so that the tested condition is always true. The instruction takes 4 cycles in the Slow clocking mode

or 2 cycles in theTurbo clocking mode.

© Parallax Inc.

CLC

CLZ

JMP W

JMP PC+W

MODE imm4

NOT W

SC

SKIP

assemblers

Equivalent Assembler Mnemonics

Syntax

support

Clear Carry bit

Clear Zero bit

Jump Indirect W

Jump Indirect W Relative

Move Immediate to MODE

Register

Complement of W

Skip if Carry bit set

Skip Next Instruction

Table 16-7: SX Equivalent Assembler Mnemonics

additional

Description

instruction

Page 39 of 51

carry), which is interpreted the same as the instruction

“clrb $03.0” (clear bit 0 in the STATUS register). Some

of the commonly supported equivalent assembler

mnemonics are described in Table 16-7.

SNB $02.0 or SB $02.0

XOR W,#$FF

Equivalent

CLRB $03.0

MOV $02,W

CLRB $03.2

ADD $02,W

MOV M,#lit

SB $03.0

4 or 3 (see Note 1)

4 or 3 (see Note 1)

1 or 2 (see Note 2)

4 or 2 (see Note 3)

Cycles

Rev 1.6 11/20/2006

www.parallax.com

1

1

1

1