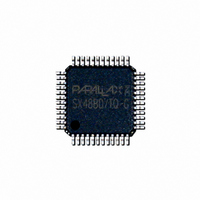

SX48BD-G Parallax Inc, SX48BD-G Datasheet

SX48BD-G

Specifications of SX48BD-G

Related parts for SX48BD-G

SX48BD-G Summary of contents

Page 1

... In-System Programming Capability and On-Chip Debug 1.0 PRODUCT OVERVIEW 1.1. Introduction The Parallax SX48BD is a member of the SX family of configurable communications controllers fabricated in an advanced CMOS process technology. The advanced process, combined with a RISC-like architecture, allows high-speed computation, flexible I/O control, and efficient data manipulation ...

Page 2

... Parallax SX48BD 1.0 Product Overview.............................................................. 1 1.1. Introduction......................................................................................1 1.2. Key Features ...................................................................................3 1.3. Architecture .....................................................................................3 1.4. Programming Benefits in Assembly and High-Level Languages......4 1.4.1. Parallax SX/B Basic Compiler......................................................................4 1.5. Programming and Debugging Support.............................................4 1.6. Applications .....................................................................................4 1.7. Support............................................................................................4 1.8. Part Numbering ...............................................................................5 2.0 Connection Diagrams ....................................................... 6 2.1. Pin Assignments..............................................................................6 2 ...

Page 3

... Parallax SX48BD 1.2. Key Features 75 MIPS Performance • MHz operation • 13.3 ns instruction cycle, 39.9 ns internal interrupt response at 75 MHz • 1 instruction per clock for most instructions (skips require 2 clocks, branches require 3 clocks, IREAD requires 4) EE/FLASH Program Memory and SRAM Data Memory • ...

Page 4

... SX’s deterministic timing. The primary technical resources for programming the SX in assembly language include the following: • The SX48BD datasheet • SX-Key Development System User’s Manual by Parallax, Inc. • Programming the SX Microcontroller – A Complete ...

Page 5

... Parallax SX48BD 1.8. Part Numbering Device Pins I/O Part# SX48BD/ SX48BD/TQ *Ratings are preliminary © Parallax Inc. Table 20-1: Ordering Information EE/Flash Voltage RAM (Bytes) (Words) Range ( 262 3.0 – 5 262 3.0 – 5.5 Page www.parallax.com Operating Temp @ Operating Temp @ 3.0 – ...

Page 6

... Parallax SX48BD 2.0 CONNECTION DIAGRAMS 2.1. Pin Assignments 2.2. Typical Connection Diagram © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 7

... Parallax SX48BD 2.3. Pin Descriptions Name Pin Type Input Levels RA0 I/O TTL/CMOS RA1 I/O TTL/CMOS RA2 I/O TTL/CMOS RA3 I/O TTL/CMOS RB0 I/O TTL/CMOS/ST RB1 I/O TTL/CMOS/ST RB2 I/O TTL/CMOS/ST RB3 I/O TTL/CMOS/ST RB4 I/O TTL/CMOS/ST RB5 I/O TTL/CMOS/ST RB6 ...

Page 8

... Parallax SX48BD 3.0 PORT DESCRIPTIONS The device contains one 4-bit port (Port A) and four 8-bit I/O ports (Port B through Port E). Port A provides symmetrical drive capability. Each port has four associated 8-bit registers (Direction, Data, TTL/CMOS Select, and Pull-Up Enable) to configure each port pin as Hi-Z input or output, to select TTL or CMOS voltage levels, and to enable/disable the weak pull-up resistor ...

Page 9

... Parallax SX48BD 3.1. Reading and Writing the Ports The five ports are memory-mapped into the data memory address space. To the CPU, the five ports are available as the RA, RB, RC, RD, and RE file registers at data memory addresses 05h through 09h, respectively. Writing to a port data register sets the voltage levels of the ...

Page 10

... Parallax SX48BD Figure 3-2: In the default device configuration, when a read is performed from a port bit position, the operation is actually reading the voltage level on the pin itself, and not the bit value stored in the port data register. This is true whether the pin is configured to operate as an input or an output ...

Page 11

... Parallax SX48BD 3.2. Read-Modify-Write Considerations When two successive instructions are used on the same I/O port (except “mov Rx,W” ) with a very high clock rate, the “write” part of one instruction might not occur soon enough before the “read” part of the very next instruction, resulting in getting “ ...

Page 12

... Parallax SX48BD MODE Reg. Mov !RA,W 00h 01h 02h 03h 04h 05h 06h 07h 08h 09h 0Ah 0Bh 0Ch 0Dh Read LVL_A 0Eh Read PLP_A 0Fh Read RA Direction 10h 11h 12h 13h 14h 15h 16h 17h 18h 19h 1Ah 1Bh 1Ch ...

Page 13

... Parallax SX48BD 3.3.2. Port Configuration Registers The port configuration registers that you control with the MOV !rx,W instruction operate as described below. RA through RE Data Direction Registers (MODE=1Fh) Each register bit sets the data direction for one port pin. Set the bit make the pin operate as a high- impedance input ...

Page 14

... Parallax SX48BD 4.0 SPECIAL-FUNCTION REGISTERS The CPU uses a set of special-function registers to control operation of the device. The CPU registers include an 8-bit working register (W), which serves as a pseudo accumulator. It holds the second operand of an instruction, receives the literal in immediate type instructions, and also can be program selected as the destination register ...

Page 15

... Parallax SX48BD 4.3. OPTION Register RTW RTW_IE RTS RTE_ES PSA Bit 7 Bit 7: RTW RTCC/W register selection Register 01h addresses Register 01h addresses RTCC Bit 6: RTE_IE RTCC interrupt enable RTCC roll-over interrupt is enabled 1 = RTCC roll-over interrupt is disabled Bit 5: RTS RTCC increment select: ...

Page 16

... Parallax SX48BD 5.0 DEVICE CONFIGURATION AND ID REGISTERS The SX device has two registers (FUSE, FUSEX) that control functions such as clock oscillator configuration. These registers are not programmable “on the fly” during normal device operation. Instead, the FUSE and FUSEX registers can only be accessed when the SX device is being programmed ...

Page 17

... Parallax SX48BD 5.2. FUSEX Word (Read/program via Programming Command) IRCTRIM2 IRCTRIM1:IRCTRIM0 SLEEPCLK IRCTRIM2: Internal RC Oscillator Trim. This 3-bit field adjusts the operation of the internal RC oscillator to make it IRCTRIM 0 operate within the target frequency range of typically 4.0 MHz. Parts are shipped from the factory untrimmed ...

Page 18

... Parallax SX48BD 6.0 MEMORY ORGANIZATION 6.1. Program Memory The program memory is organized as 4K, 12-bit wide words. The program memory words are addressed sequentially by a binary program counter. Upon reset, the program counter is initialized with 0FFFh. If there is no branch operation, it will increment to the maximum value possible for the device and roll over and begin again ...

Page 19

... Parallax SX48BD © Parallax Inc. Figure 6-1: Register Access Modes Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 20

... Parallax SX48BD 6.2.2. Register Access Examples Here is an example of an instruction that uses direct addressing: inc $0F ;increment file register 0Fh This instruction increments the contents of file register 0Fh in the global register bank. It does not matter what is contained in the FSR register. To gain access to any register outside of the global register bank necessary to use semi-direct or indirect addressing ...

Page 21

... Parallax SX48BD 7.0 POWER DOWN MODE The power down mode is entered by executing the SLEEP instruction. In power down mode, only the Watchdog Timer (WDT) and SLEEPCLOCK are active, if enabled. The operation clock can be enabled or disabled during this mode, by using the SLEEPCLK bit of the FUSEX register. If the ...

Page 22

... Parallax SX48BD Figure 7-1: Multi-Input Wakeup Block Diagram © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 23

... Parallax SX48BD 7.2. Port B MIWU/Interrupt Configuration The WKPND_B register comes up with an unknown value upon reset. The user program must clear the register prior to enabling the wake-up condition or interrupts. The proper initialization sequence is: Select the desired edge (through WKED_B register). Clear the WKPND_B register. ...

Page 24

... Parallax SX48BD 8.0 INTERRUPT SUPPORT The device supports both internal and external maskable interrupts. The internal interrupt is generated as a result of the RTCC rolling over from FFh to 00h. This interrupt source has an associated enable bit located in the OPTION register and pending flag bit in the Timer T1 Control B register ...

Page 25

... Parallax SX48BD All interrupts are global in nature; that is, no interrupt has priority over another. Interrupts are handled sequentially. Figure 8-2 shows the interrupt processing sequence. Once an interrupt is acknowledged, all subsequent interrupts are disabled until return from servicing the current interrupt. The PC is pushed onto the single level interrupt stack, and ...

Page 26

... Parallax SX48BD 9.0 OSCILLATOR CIRCUITS The device supports several user-selectable oscillator modes. The oscillator modes are selected by programming the appropriate values into the FUSE Word register. These are the different oscillator modes offered: • LP: Low Power Crystal • XT: Crystal/Resonator • HS: High Speed Crystal/Resonator/Clock Oscillator • ...

Page 27

... Parallax SX48BD Table 9-2: External Component Selection for Murata Ceramic Resonators (V FOSC2:FOSC0 Frequency 011 4 MHz CSA4.00MG 011 4 MHz CST4.00MGW 011 4 MHz CSTCC4.00G0H6 011 8 MHz CSA8.00MTZ 011 8 MHz CST8.00MTW 011 8 MHz CSTCC8.00MG0H6 011 20 MHz CSA20.00MXZ040 011 20 MHz CST20.00MXW0H1 011 20 MHz CSACV20.00MXJ040 011 20 MHz CSTCV20 ...

Page 28

... SX, we have specified a custom TTL oscillator that performs well throughout the industrial temperature range. Figure 9-3 depicts how the SX is used with the Transko 75MHz TTL oscillator. Figure 9-3: SX48BD with 75 MHz TTL Oscillator Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 29

... Parallax SX48BD 9.3. External RC Mode The external RC oscillator mode provides a cost-effective approach for applications that do not require a precise operating frequency. In this mode, the RC oscillator frequency is a function of the supply voltage, the resistor (R) and capacitor (C) values, and the operating temperature. In addition, the oscillator frequency will vary from unit to unit due to normal manufacturing process variations ...

Page 30

... Parallax SX48BD 10.0 REAL TIME CLOCK/COUNTER (RTCC)/WATCHDOG TIMER The device contains an 8-bit Real Time Clock/Counter (RTCC) and an 8-bit Watchdog Timer (WDT). An 8-bit programmable prescaler extends the RTCC to 16 bits. If the prescaler is not used for the RTCC, it can serve as a postscaler for the Watchdog Timer. Figure 10-1 shows the RTCC and WDT block diagram ...

Page 31

... Parallax SX48BD © Parallax Inc. Figure 10-1: RTCC and WDT Block Diagram Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 32

... Parallax SX48BD 11.0 MULTI-FUNCTION TIMERS The device contains two independent 16-bit multi-func tion timers, designated T1 and T2. These versatile, programmable timers reduce the software burden on the CPU in real-time control applications such as PWM generation, motor control, triac control, variable- brightness display control, sine wave generation, and data acquisition ...

Page 33

... Parallax SX48BD 11.1. Timer Registers Each timer consists of several registers. Timer T1 registers: T1CPL - Lower byte of Timer T1 capture register T1CPH - Higher byte of Timer T1 capture register T1R1CML - Lower byte of Timer T1 compare register 1 T1R1CMH - Higher byte of Timer T1 compare register 1 T1R2CML - Lower byte of Timer T1 compare register 2 ...

Page 34

... Parallax SX48BD count upward after a match occurs (unlike the PWM mode, which resets the counter to zero when a match occurs). In the Capture/Compare mode, the timer is clocked by the on-chip system clock divided by a value defined bit divide-by factor. The divide-by factor can be set to any power-of-2 from 1 to 128 ...

Page 35

... Parallax SX48BD Timer T1 Control B Register (T1CNTB) RTCCOV T1CPEDG T1EXEDG 7 6 RTCCOV RTCC Overflow Flag. This flag is automatically set to 1 when the Real-Time Clock/Counter (RTCC) overflows from FFh to 00h. This flag stays set until it is cleared by the software. Note that this flag is not related to Multi-function timers T1 and T2 ...

Page 36

... Parallax SX48BD Timer T2 Control A Register (T2CNTA) T2CPF2 T2CPF1 T2CPIE 7 6 T2CPF2 Timer T2 Capture Flag 2. In Capture/Compare mode, this flag is automatically set to 1 when a capture event occurs on the Capture 2 pin of Timer T2 (pin RC1). It stays set until cleared by the software. T2CPF1 Timer T2 Capture Flag 1. In Capture/Compare mode, this flag is automatically set to 1 when a capture event occurs on the Capture 1 pin of Timer T2 (pin RC1) ...

Page 37

... Parallax SX48BD Timer T2 Control b Register (T2CNTb) PRTRD T2CPEDG T2EXEDG 7 6 PORTRD Port Read mode. This bit determines how the device reads data from its I/O ports (Port A through Port E). Clear this bit have the device read data from the port I/O pins directly. Set this bit have the device read data from the port data registers ...

Page 38

... Parallax SX48BD 12.0 COMPARATOR The device contains an on-chip differential comparator. Ports RB0-RB2 support the comparator. Pins RB1 and RB2 are the comparator negative and positive inputs, respectively, while RB0 serves as the comparator output pin. To use these pins in conjunction with the comparator, the user program must configure RB1 and RB2 as inputs and RB0 as an output ...

Page 39

... Parallax SX48BD 13.0 RESET Power-On Reset, Brown-Out Reset, Watchdog Reset, or External Reset initializes the device. Each one of these reset conditions causes the program counter to branch to the top of the program memory. For example, on the device with 4096 K ($1000 hex) words of program memory, the program counter is initialized to 0FFF upon a valid reset condition ...

Page 40

... Parallax SX48BD Figure 13-3 shows the on-chip Power-On Reset sequence where the MCLR pin is tied Note: connecting the MCLR pin directly to the V supply is not recommended. If the V before the DRT timeout period expires, the device will receive a proper reset. However, Figure 13-4 depicts a situation where V rises too slowly ...

Page 41

... Parallax SX48BD 15.0 REGISTER STATES UPON DIFFERENT RESET CONDITIONS The effect of different reset operations on a register depends on the register and the type of reset operation. Some registers are initialized to specific values, some are left unchanged, some are undefined, and some are initialized to an unknown value. ...

Page 42

... Parallax SX48BD 16.0 INSTRUCTION SET As mentioned earlier, the SX family of devices uses a modified Harvard architecture with memory-mapped input/output. The device also has a RISC type architecture in that there are 43 single-word basic instructions. The instruction set contains byte-oriented file register, bit-oriented file register, and literal/control instructions. ...

Page 43

... Parallax SX48BD 16.3. Addressing Modes The device support the following addressing modes: • Data Direct • Data Indirect • Data Semidirect • Immediate • Program Direct • Program Indirect • Relative Both direct and indirect addressing modes are available. The INDF register, though physically not implemented, is used in conjunction with the indirect data pointer (FSR) to perform indirect addressing ...

Page 44

... Parallax SX48BD 16.7. Increment/Decrement The current selected bank of 31 registers serves as a set of accumulators. The instruction set contains instructions to increment and decrement the register file. The device also includes both INCSZ fr (increment file register and skip if zero) and DECSZ fr (decrement file register and skip if zero) instructions ...

Page 45

... Parallax SX48BD 16.11. Subroutine Operation 16.11.1. Push Operation When a subroutine is called, the return address is pushed onto the subroutine stack. Specifically, each address in the stack is moved to the next lower level in order to make room for the new address to be stored. Stack 1 receives the contents of the program counter. Stack 8 is overwritten with what was in Stack 7 ...

Page 46

... Parallax SX48BD 16.16. Key to Abbreviations and Symbols Table 16-1: Key to Abbreviations and Symbols Symbol Description W Working register fr File register (memory mapped in range of 00h to FFh) PC Lower eight bits of program counter (file register 02h) STATUS STATUS register (file register 03h) FSR File Select Register (file register 04h) ...

Page 47

... Parallax SX48BD 17.0 NATIVE INSTRUCTION SET SUMMARY TABLES Table 17-1 through Table 17-6 list all of the native assembly instructions, organized by category. For each instruction, the table shows the instruction mnemonic (as written in assembly language), a brief description of what the instruction does, the number of clock cycles required for execution, the binary opcode, and the status flags affected by the instruction ...

Page 48

... Parallax SX48BD Table 17-2: Native SX Instruction Set: Arithmetic and Shift Operations Mnemonic, Description Operands Add ( W); carry bit is added if CF ADD fr,W bit in FUSEX register is cleared to 0 Add +fr); carry bit is added if CF ADD W,fr bit in FUSEX register is cleared to 0 CLR fr Clear fr ( CLR W ...

Page 49

... Parallax SX48BD Table 17-4: Native SX Instruction Set: Data Movement Instructions Mnemonic, Description Operands MOV fr,W Move ( MOV W,fr Move fr) Move (fr- fr-W); complement of MOV W,fr-W carry bit is subtracted if CF bit in FUSEX register is cleared to 0 MOV W,#lit Move Literal lit) MOV W,/fr Move Complement FFh) MOV W,--fr Move (fr – ...

Page 50

... Parallax SX48BD Table 17-5: Native SX Instruction Set: Program Control Instructions Mnemonic, Description Operands Call Subroutine: Top-of-stack = program counter + 1 CALL addr8 PC(7:0) = addr8 Program counter ( Program counter (10:9) = PA1:PA0 Jump to Address: PC(7:0) = addr9(7:0) JMP addr9 Program counter = (8) = addr9(8) Program counter (10:9) = PA1:PA0 ...

Page 51

... Parallax SX48BD 17.1. Equivalent Assembler Mnemonics Some assemblers support additional mnemonics that are special cases of existing instructions or alternative mnemonics for standard ones. For example, an assembler might support the mnemonic “CLC” (clear Table 17-7: SX Equivalent Assembler Mnemonics Syntax CLC Clear Carry bit ...

Page 52

... Parallax SX48BD 18.0 ELECTRICAL CHARACTERISTICS 18.1. Absolute Maximum Ratings Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the remainder of Section 18 ...

Page 53

... Parallax SX48BD 18.2. DC Characteristics SX48BD running at 50 MHz: Operating Temperature - 40 °C <= Ta <= +85 °C (Industrial) Symbol Parameter Supply Voltage rise rate to ensure dd S Vdd Power-On Reset (Note 2) Supply Current, active I dd Crystal oscillator (Note 3) Supply Current, power down I pd Input Levels ...

Page 54

... Parallax SX48BD 18.3. AC Characteristics SX48BD running at 50 MHz: Operating Temperature - 40 °C <= Ta <= +85 °C (Industrial) Symbol Parameter External CLKIN Frequency F osc Oscillator Frequency (Crystal/Resonator) External CLKIN Period T osc Oscillator Period (Crystal/Resonator) Clock in (OSC1) Low or High Time osL osH Note: Data in the Typical (“TYP”) column °C unless otherwise stated. ...

Page 55

... Parallax SX48BD 18.5. Typical Performance Characteristics (25 °C) © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 56

... Parallax SX48BD 17.5. Typical Performance Characteristics (25 °C) (Continued) © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 57

... Parallax SX48BD 17.5. Typical Performance Characteristics (25 °C) (Continued) © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 58

... Parallax SX48BD 19.0 PACKAGE DIMENSIONS © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 59

... Parallax Research and Development team, contact Parallax Sales or Tech Support. Sales/Tech Support: (916) 624-8333 Toll Free in the US: 1-888-512-1024 Sales: sales@parallax.com Tech Support: support@parallax.com Page www.parallax.com unbiased HAST Stock Code Tested SX20AC/SS-G 20 SX28AC/SS-G 20 SX28AC/DP-G 17 SX48BD-G 20 Subtotal 77 SX20AC/SS-G 20 SX28AC/SS-G 20 SX28AC/DP-G 17 SX48BD-G 20 Subtotal 77 Rev 1.5 192 hours, Passed 11/20/2006 ...

Page 60

... Parallax SX48BD © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...

Page 61

... Parallax SX48BD © Parallax Inc. Page www.parallax.com Rev 1.5 11/20/2006 ...