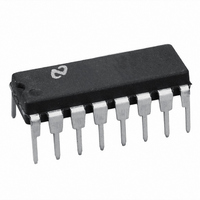

COP8SAA716N9 National Semiconductor, COP8SAA716N9 Datasheet - Page 33

COP8SAA716N9

Manufacturer Part Number

COP8SAA716N9

Description

IC MCU OTP 8BIT 1K 16DIP

Manufacturer

National Semiconductor

Series

COP8™ 8SAr

Datasheet

1.COP8-PGMA-28CSP.pdf

(60 pages)

Specifications of COP8SAA716N9

Core Processor

COP8

Core Size

8-Bit

Speed

10MHz

Connectivity

Microwire/Plus (SPI)

Peripherals

POR, PWM, WDT

Number Of I /o

12

Program Memory Size

1KB (1K x 8)

Program Memory Type

OTP

Ram Size

64 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

16-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Data Converters

-

Other names

*COP8SAA716N9

COP8SAA716N9B

COP8SAA716N9B

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

9.0 Interrupts

9.4 NON-MASKABLE INTERRUPT

9.4.1 Pending Flag

There is a pending flag bit associated with the non-maskable

interrupt, called STPND. This pending flag is not

memory-mapped and cannot be accessed directly by the

software.

The pending flag is reset to zero when a device Reset

occurs. When the non-maskable interrupt occurs, the asso-

ciated pending bit is set to 1. The interrupt service routine

should contain an RPND instruction to reset the pending flag

to zero. The RPND instruction always resets the STPND

flag.

9.4.2 Software Trap

The Software Trap is a special kind of non-maskable inter-

rupt which occurs when the INTR instruction (used to ac-

knowledge interrupts) is fetched from program memory and

placed in the instruction register. This can happen in a

variety of ways, usually because of an error condition. Some

examples of causes are listed below.

If the program counter incorrectly points to a memory loca-

tion beyond the available program memory space, the

non-existent or unused memory location returns zeroes

which is interpreted as the INTR instruction.

If the stack is popped beyond the allowed limit (address 02F

or 06F Hex), a Software Trap is triggered.

A Software Trap can be triggered by a temporary hardware

condition such as a brownout or power supply glitch.

The Software Trap has the highest priority of all interrupts.

When a Software Trap occurs, the STPND bit is set. The GIE

bit is not affected and the pending bit (not accessible by the

user) is used to inhibit other interrupts and to direct the

program to the ST service routine with the VIS instruction.

Nothing can interrupt a Software Trap service routine except

for another Software Trap. The STPND can be reset only by

the RPND instruction or a chip Reset.

The Software Trap indicates an unusual or unknown error

condition. Generally, returning to normal execution at the

point where the Software Trap occurred cannot be done

reliably. Therefore, the Software Trap service routine should

reinitialize the stack pointer and perform a recovery proce-

dure that restarts the software at some known point, similar

to a device Reset, but not necessarily performing all the

same functions as a device Reset. The routine must also

execute the RPND instruction to reset the STPND flag.

Otherwise, all other interrupts will be locked out. To the

extent possible, the interrupt routine should record or indi-

cate the context of the device so that the cause of the

Software Trap can be determined.

If the user wishes to return to normal execution from the

point at which the Software Trap was triggered, the user

must first execute RPND, followed by RETSK rather than

RETI or RET. This is because the return address stored on

the stack is the address of the INTR instruction that triggered

the interrupt. The program must skip that instruction in order

to proceed with the next one. Otherwise, an infinite loop of

Software Traps and returns will occur.

(Continued)

33

Programming a return to normal execution requires careful

consideration. If the Software Trap routine is interrupted by

another Software Trap, the RPND instruction in the service

routine for the second Software Trap will reset the STPND

flag; upon return to the first Software Trap routine, the

STPND flag will have the wrong state. This will allow

maskable interrupts to be acknowledged during the servicing

of the first Software Trap. To avoid problems such as this, the

user program should contain the Software Trap routine to

perform a recovery procedure rather than a return to normal

execution.

Under normal conditions, the STPND flag is reset by a

RPND instruction in the Software Trap service routine. If a

programming error or hardware condition (brownout, power

supply glitch, etc.) sets the STPND flag without providing a

way for it to be cleared, all other interrupts will be locked out.

To alleviate this condition, the user can use extra RPND

instructions in the main program and in the WATCHDOG

service routine (if present). There is no harm in executing

extra RPND instructions in these parts of the program.

9.5 PORT L INTERRUPTS

Port L provides the user with an additional eight fully select-

able, edge sensitive interrupts which are all vectored into the

same service subroutine.

The interrupt from Port L shares logic with the wake up

circuitry. The register WKEN allows interrupts from Port L to

be individually enabled or disabled. The register WKEDG

specifies the trigger condition to be either a positive or a

negative edge. Finally, the register WKPND latches in the

pending trigger conditions.

The GIE (Global Interrupt Enable) bit enables the interrupt

function.

A control flag, LPEN, functions as a global interrupt enable

for Port L interrupts. Setting the LPEN flag will enable inter-

rupts and vice versa. A separate global pending flag is not

needed since the register WKPND is adequate.

Since Port L is also used for waking the device out of the

HALT or IDLE modes, the user can elect to exit the HALT or

IDLE modes either with or without the interrupt enabled. If he

elects to disable the interrupt, then the device will restart

execution from the instruction immediately following the in-

struction that placed the microcontroller in the HALT or IDLE

modes. In the other case, the device will first execute the

interrupt service routine and then revert to normal operation.

(See HALT MODE for clock option wakeup information.)

9.6 INTERRUPT SUMMARY

The device uses the following types of interrupts, listed

below in order of priority:

1. The Software Trap non-maskable interrupt, triggered by

2. Maskable interrupts, triggered by an on-chip peripheral

the INTR (00 opcode) instruction. The Software Trap is

acknowledged immediately. This interrupt service rou-

tine can be interrupted only by another Software Trap.

The Software Trap should end with two RPND instruc-

tions followed by a restart procedure.

block or an external device connected to the device.

Under ordinary conditions, a maskable interrupt will not

interrupt any other interrupt routine in progress. A

maskable interrupt routine in progress can be inter-

rupted by the non-maskable interrupt request. A

maskable interrupt routine should end with an RETI

instruction.

www.national.com