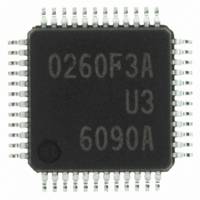

M30260F3AGP#U3 Renesas Electronics America, M30260F3AGP#U3 Datasheet - Page 164

M30260F3AGP#U3

Manufacturer Part Number

M30260F3AGP#U3

Description

IC M16C/TINY MCU FLASH 48LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/26r

Specifications of M30260F3AGP#U3

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, PWM, Voltage Detect, WDT

Number Of I /o

39

Program Memory Size

24KB (24K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 164 of 354

- Download datasheet (4Mb)

R

R

M

e

E

. v

1

J

Figure 13.1.1.1. Typical transmit/receive timings in clock synchronous serial I/O mode

0

6

2

9

C

0 .

B

2 /

0

0

2

6

0

A

F

The above timing diagram applies to the case where the register bits are set as follows:

2

Transfer clock

UiC1 register

TE bit

UiC1 register

TI bit

CTSi

CLKi

TxDi

UiC0 register

TXEPT bit

SiTIC register

IR bit

e

The above timing diagram applies to the case where the register bits are set

as follows:

f

(2) Example of Receive Timing (External clock is selected)

• The CKDIR bit in the UiMR register is set to "0" (internal clock)

• The CRD bit in the UiC0 register is set to "0" (CTS/RTS enabled); CRS bit is set to "0" (CTS selected)

• The CKPOL bit in the UiC0 register is set to "0" (transmit data output at the falling edge and receive data taken in at the rising edge of the

• The UiIRS bit is set to "0" (an interrupt request occurs when the transmit buffer becomes empty): U0IRS bit is the bit 0 in the UCON register

EXT

(1) Example of Transmit Timing (Internal clock is selected)

0 -

G

b

transfer clock)

U1IRS bit is the bit 1 in the UCON register, and U2IRS bit is the bit 4 in the U2C1 register.

• The CKDIR bit in the UiMR register is set to "1" (external clock)

• The CRD bit in the UiC0 register is set to "0"(CTS/RTS enabled);

• UiC0 register CKPOL bit is set to "0"(transmit data output at the falling edge and

UiC1 register

RE bit

UiC1 register

TE bit

UiC1 register

TI bit

RTSi

CLKi

RxDi

UiC1 register

RI bit

SiRIC register

IR bit

The CRS bit is set to "1" (RTS selected)

receive data taken in at the rising edge of the transfer clock)

1 .

2

o r

: frequency of external clock

0

, 5

u

0

p

2

0

(

0

M

7

1

6

C

“H”

page 145

“1”

“0”

“1”

“0”

“L”

“1”

“0”

“1”

“0”

2 /

“H”

“L”

“1”

“0”

“1”

“0”

“1”

“0”

“1”

“0”

“1”

“0”

6

, A

Transferred from UARTi receive register

Write data to the UiTB register

M

D

1

f o

0

6

D

Transferred from UiTB register to UARTi transmit register

Write dummy data to UiTB register

0

3

D

C

1

2

D

2 /

9

1

T

D

6

CLK

2

D

, B

D

2

to UiRB register

3

Transferred from UiTB register to UARTi transmit register

D

M

3

D

Tc

4

1

D

4

6

D

1 / f

Receive data is taken in

Cleared to “0” when interrupt request is accepted, or cleared to “0” in a program

5

C

D

5

Cleared to “0” when interrupt request is

accepted, or cleared to “0” by program

D

2 /

EXT

6

D

6

6

D

) T

7

D

Stopped pulsing because CTSi = “H”

7

Read out from UiRB register

D

0

D

0

D

Even if the reception is completed, the RTS

does not change. The RTS becomes “L”

when the RI bit changes to “0” from “1”.

Tc = T

1

D

D

1

2

fj: frequency of UiBRG count source (f

n: value set to UiBRG register

D

i: 0 to 2

CLK

D

2

3

D

Make sure the following conditions are met when input

to the CLKi pin before receiving data is high:

D

3

= 2(n + 1) / fj

• UiC0 register TE bit is set to "1" (transmit enabled)

• UiC0 register RE bit is set to "1" (Receive enabled)

• Write dummy data to the UiTB register

4

D

4

D

5

D

D

5

6

D

7

Stopped pulsing because the TE bit = “0”

D

0

D

1

D

1SIO

2

D

, f

3

2SIO

D

4

, f

D

8SIO

5

13. Serial I/O

D

6

, f

32SIO

D

7

)

Related parts for M30260F3AGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: