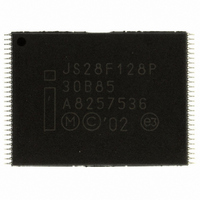

JS28F128P30B85A NUMONYX, JS28F128P30B85A Datasheet - Page 42

JS28F128P30B85A

Manufacturer Part Number

JS28F128P30B85A

Description

IC FLASH 128MBIT 85NS 56TSOP

Manufacturer

NUMONYX

Series

StrataFlash™r

Datasheet

1.RD48F4400P0VBQEJ.pdf

(97 pages)

Specifications of JS28F128P30B85A

Format - Memory

FLASH

Memory Type

FLASH

Memory Size

128M (8Mx16)

Speed

85ns

Interface

Parallel

Voltage - Supply

1.7 V ~ 2 V

Operating Temperature

-40°C ~ 85°C

Package / Case

56-TSOP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

873810

873810

JS28F128P30B85

JS28F128P30B85 873810

873810

JS28F128P30B85

JS28F128P30B85 873810

Table 19: Read Configuration Register Description (Sheet 2 of 2)

11.2.1

11.2.2

Datasheet

42

13:11

10

9

8

7

6

5:4

3

2:0

Note:

Latency Code 2, Data Hold for a 2-clock data cycle (DH = 1) WAIT must be deasserted with valid data (WD = 0).

Latency Code 2, Data Hold for a 2-cock data cycle (DH=1) WAIT deasserted one data cycle before valid data (WD = 1)

combination is not supported.

shown using the QUAD+ package. For EASY BGA and TSOP packages, the table reference should be adjusted using

address bits A[16:1].

Latency Count (LC[2:0])

Wait Polarity (WP)

Data Hold (DH)

Wait Delay (WD)

Burst Sequence (BS)

Clock Edge (CE)

Reserved (R)

Burst Wrap (BW)

Burst Length (BL[2:0])

Read Mode

The Read Mode (RM) bit selects synchronous burst-mode or asynchronous page-mode

operation for the device. When the RM bit is set, asynchronous page mode is selected

(default). When RM is cleared, synchronous burst mode is selected.

Latency Count

The Latency Count (LC) bits tell the device how many clock cycles must elapse from the

rising edge of ADV# (or from the first valid clock edge after ADV# is asserted) until the

first valid data word is to be driven onto DQ[15:0]. The input clock frequency is used to

determine this value and

settings of LC. The maximum Latency Count for P30 would be Code 4 based on the Max

Clock frequency specification of 52 mhz, and there will be zero WAIT States when

bursting within the word line. Please also refer to

Considerations” on page 47

Refer to

Code Settings.

Table 20, “Latency Count (LC) and Frequency Support” on page 43

Table 19, “Read Configuration Register Description” on page 41

010 =Code 2

011 =Code 3

100 =Code 4

101 =Code 5

110 =Code 6

111 =Code 7 (default)

(Other bit settings are reserved)

0 =WAIT signal is active low

1 =WAIT signal is active high (default)

0 =Data held for a 1-clock data cycle

1 =Data held for a 2-clock data cycle (default)

0 =WAIT deasserted with valid data

1 =WAIT deasserted one data cycle before valid data (default)

0 =Reserved

1 =Linear (default)

0 = Falling edge

1 = Rising edge (default)

Reserved bits should be cleared (0)

0 =Wrap; Burst accesses wrap within burst length set by BL[2:0]

1 =No Wrap; Burst accesses do not wrap within burst length (default)

001 =4-word burst

010 =8-word burst

011 =16-word burst

111 =Continuous-word burst (default)

(Other bit settings are reserved)

Figure 13

for more information on EOWL.

shows the data output latency for the different

“End of Word Line (EOWL)

for Latency

August 2008

306666-12

is

P30