MT9P031I12STC Aptina LLC, MT9P031I12STC Datasheet - Page 4

MT9P031I12STC

Manufacturer Part Number

MT9P031I12STC

Description

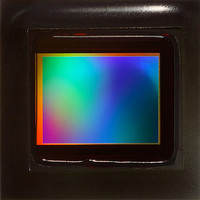

IC, IMAGE SENSOR, 2.2 X 2.2µM, ILCC-48

Manufacturer

Aptina LLC

Type

CMOS Imagingr

Datasheets

1.MT9P031I12STCH_ES.pdf

(6 pages)

2.MT9P031I12STCH_ES.pdf

(12 pages)

3.MT9P031I12STCH_ES.pdf

(2 pages)

Specifications of MT9P031I12STC

Active Pixel Size

2592 X 1944

Pixel Size (h X W)

2.2 X 2.2

Frame Rate Per Sec

15

Color

RGB

Sensor Case Style

LCC

No. Of Pins

48

Supply Voltage Range

1.7V To 3.1V

Pixel Size

2.2µm x 2.2µm

Active Pixel Array

2592H x 1944V

Frames Per Second

60

Voltage - Supply

2.6 V ~ 3.1 V

Package / Case

48-iLCC

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

557-1260 - KIT HEAD BOARD FOR MT9P031557-1258 - KIT DEV FOR MT9P031

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

557-1262

MT9P031I12STC

Q3873226

MT9P031I12STC

Q3873226

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MT9P031I12STC

Manufacturer:

APTINA

Quantity:

1 000

Company:

Part Number:

MT9P031I12STC

Manufacturer:

APTINA

Quantity:

8 555

Part Number:

MT9P031I12STC

Manufacturer:

APTINA

Quantity:

20 000

Company:

Part Number:

MT9P031I12STCES

Manufacturer:

ProMOS

Quantity:

346

Company:

Part Number:

MT9P031I12STCH ES

Manufacturer:

Aptina LLC

Quantity:

135

Operational Description

Board Functionality

Figure 3:

DEMO2

PDF: 09005aef82ca4ad2/Source: 09005aef82ca8484

demobrief.fm - Rev. B 7/07 EN

Sensor Head

FRAME_VALID

Connector

Interface

LINE_VALID

DEMO2 Board Block Diagram

Sensor

26-Pin

PIXCLK

JTAG

Download

10

Program

FPGA

The USB board provides centralized communication between the image sensor and the

host PC. The system receives firmware programming from a serial EEPROM that config-

ures the board into a synchronous slave FIFO mode. The sensor data fills up an internal

FIFO with data when the elimination of handshake is taking place. The firmware auto-

matically sends data through the USB 2.0 interface whenever the FIFO becomes full and

the FRAME_VALID is polled to determine when a frame is complete. When the

FRAME_VALID drops, the host computer is signaled through the USB interface with a

frame end packet. The firmware also supplies the necessary code to implement USB

vendor commands that allow the host computer to query and modify the system config-

uration data.

Vendor commands are used to communicate with the image sensor through the serial

host interface protocol built into the sensor head interface.

Micron’s DEMO2 board comes equipped with the addition of an FPGA and memory

controller. This allows the hardware to store up to three entire frames of data on the

board prior to USB 2 transport, which is important for large resolution sensors to avoid

dropping frames. The DEMO2 baseboards are common to all sensor configurations. The

FPGA optimizes the data flow through the USB, such that the FIFOs never overflow and

complete frames are guaranteed even for large sensors.

EEPROM

WR Control

Buffer

Input

Generator

Timing

30

Low-Power

Controller

32

Microm

SDRAM

RAM

4

30

Controller

Sync.

USB

RD Control

Micron Technology, Inc., reserves the right to change products or specifications without notice.

Output

Buffer

Image Sensor Demo System Kits

FX_FULL

LINE_OUT

FRAME_OUT

IF_CLOCK

16

Operational Description

Controller

Chip

USB

©2006 Micron Technology, Inc. All rights reserved.

Channel

to PC

USB