DP8570AV National Semiconductor, DP8570AV Datasheet

DP8570AV

Specifications of DP8570AV

Available stocks

Related parts for DP8570AV

DP8570AV Summary of contents

Page 1

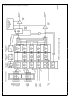

... Power failure logic and control functions have been integrat chip This logic is used by the TCP to issue a power fail Block Diagram TRI-STATE is a registered trademark of National Semiconductor Corporation C 1995 National Semiconductor Corporation TL F 8638 interrupt and lock out the p interface The time power fails ...

Page 2

... Absolute Maximum Ratings If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage ( Input Voltage ( Output Voltage ( OUT Storage Temperature Range Power Dissipation (PD) Lead Temperature (Soldering 10 sec ) DC Electrical Characteristics PFAIL l ...

Page 3

AC Electrical Characteristics PFAIL Symbol READ TIMING t Address Valid Prior to Read Strobe AR t Read Strobe Width (Note Chip Select to Data Valid ...

Page 4

Timing Waveforms Read Timing Diagram Write Timing Diagram 8638 – 8638 – 25 ...

Page 5

... GND This is the common ground power pin for both V and V CC Connection Diagrams Dual-In-Line Order Number DP8570AN See NS Package Number N28B Plastic Chip Carrier Utiliz- Top View BB Order Number DP8570AV See NS Package Number V28A 5 The T1 pin is con 8638 – 5 Top View ...

Page 6

Functional Description The DP8570A contains a fast access real time clock two 10 MHz 16-bit timers interrupt control logic power fail detect logic and CMOS RAM All functions of the TCP are con- trolled by a set of nine registers ...

Page 7

Functional Description (Continued) INITIAL POWER-ON of BOTH V and and V may be applied in any sequence In order for BB CC the power fail circuitry to function correctly whenever power is off the V pin ...

Page 8

Functional Description (Continued) The oscillator is programmed via the Real Time Mode Reg- ister to operate at various frequencies The crystal oscillator is designed to offer optimum performance at each frequen- cy Thus at 32 768 kHz the oscillator is ...

Page 9

Functional Description (Continued) Interrupts Fall Into Four Categories 1 The Timer Interrupts For description see Timer Section 2 The Alarm Compare Interrupt Issued when the value in the time compared RAM equals the counter 3 The Periodic Interrupts These are ...

Page 10

Functional Description (Continued) 10 ...

Page 11

Functional Description (Continued) FIGURE 6 System-Battery Switchover (Upper Left) Power Fail The user may choose to have this power failed signal lock- out the TCP’s data bus within 30 s min 63 delay the lock-out to enable P access after ...

Page 12

Functional Description (Continued) the chip is unlocked but only after another 30 s min 63 s max debounce time The system designer must en- sure that his system is stable when power has returned The power fail circuitry contains active ...

Page 13

Functional Description (Continued) INPUT CLOCK SELECTION The input frequency to the timers may be selected Each timer has a prescaler that gives a wide selection of clocking rates In addition the DP8570A has a single external clock input pin that ...

Page 14

Functional Description (Continued) of the input data registers are loaded into the timer The output will stay high until the counter reaches zero At zero the output is reset The result is an output pulse whose du- ration is equal ...

Page 15

Functional Description (Continued) FIGURE 10 Timing Waveforms for Timer Mode 2 (Timer Output Programmed Active High) MODE 3 RETRIGGERABLE ONE SHOT This mode is different from the previous three modes in that this is the only mode which uses the ...

Page 16

Functional Description (Continued) TABLE VII Register Counter RAM Addressing for DP8570A PS RS A0-4 Description (Note 1) (Note 2) CONTROL REGISTERS Main Status Register Timer 0 Control Register Timer 1 Control ...

Page 17

Functional Description (Continued) TIMER 0 AND 1 CONTROL REGISTER These registers control the operation of the timers Each timer has its own register D0 This bit will Start (1) or Stop (0) the timer When the timer is stopped the ...

Page 18

Functional Description (Continued) D5 The Delay Enable bit is used when a power fail occurs If this bit is set a 480 s delay is generated internally before the P interface is locked out This will enable the access the ...

Page 19

Functional Description (Continued) D0 This bit when set to a one makes the T1 (timer 1) output pin active high and when set to a zero it makes this pin active low D1 This bit controls whether the T1 pin ...

Page 20

Control and Status Register Address Bit Map Main Status Register ADDRESS Page Register Timer 1 Select Select Interrupt Timer 0 Control Register PS 0 ...

Page 21

Application Hints Suggested Initialization Procedure for DP8570A in bat- tery backed applications that use the Enter the test mode by writing bit D7 in the Period- ic Flag Register 2 Write zero to the ...

Page 22

Appendix A FIGURE A1 Typical Interface Where the ‘‘Write Strobe’’ is Synchronized to the Decrementing Clock of the Timer 8638– 30 ...

Page 23

Typical Performance Characteristics Operating Current vs Supply Voltage (Single Supply Mode F 32 768 kHz) e OSC Standby Current vs Power Supply Voltage (F 32 768 kHz) e OSC Operating Current vs Supply Voltage (Battery Backed Mode F e OSC ...

Page 24

24 ...

Page 25

Physical Dimensions inches (millimeters) Molded Dual-In-Line Package (N) Order Number DP8570AN NS Package Number N28B 25 ...

Page 26

... National does not assume any responsibility for use of any circuitry described no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications Plastic Chip Carrier Package (V) Order Number DP8570AV NS Package Number V28A 2 A critical component is any component of a life ...