HCPL-0601 Fairchild Semiconductor, HCPL-0601 Datasheet

HCPL-0601

Specifications of HCPL-0601

Available stocks

Related parts for HCPL-0601

HCPL-0601 Summary of contents

Page 1

... Line receiver, data transmission • Data multiplexing • Switching power supplies • Pulse transformer replacement • Computer-peripheral interface Input 0.1 µF bypass capacitor must be connected between pins 8 and 5. (See note 1) © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 V N 0.143 (3.63 0.123 (3.13 ...

Page 2

... Operating Temperature Fan Out (TTL load) *6 guard banded value which allows for at least 20% CTR degradation. Initial input current threshold value is 5 less © 2004 Fairchild Semiconductor Corporation HIGH SPEED-10 MBit/s LOGIC GATE OPTOCOUPLERS HCPL-0601 (No derating required up to 85°C) Symbol T STG T OPR ...

Page 3

... 350 , pF (Note 7) (Fig. 13 7 350 , pF (Note 8) (Fig. 13) = 350 ) (T =25° HCPL-0600 (Min HCPL-0601 CM (Note 9)(Fig. 14) = 350 ) (T =25° HCPL-0600 (Max HCPL-0601 CM (Note 10)(Fig. 14) Page HIGH SPEED-10 MBit/s Symbol Min Typ** Max 1 1. VF CCH CCL I -0.8 -1 -0 0.8 ...

Page 4

... V). Measured in volts per microsecond (V/µs). OUT 11. Device considered a two-terminal device: Pins 1,2,3 and 4 shorted together, and Pins 5,6,7 and 8 shorted together. © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 (T = -40°C to +85°C Unless otherwise specified.) A Test Conditions ...

Page 5

... V - FORWARD VOLTAGE (V) F Fig. 3 Input Threshold Current vs. Temperature 0. 350 -40 - TEMPERATURE (˚C) A © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 - 1.5 1.6 1.7 Fig. 4 High Level Output Current vs. Temperature - 100 Page HIGH SPEED-10 MBit/s Fig. 2 Output Voltage vs. Forward Current ...

Page 6

... Fig. 7 Propagation Delay vs. Temperature 100 7.5mA PLH PLH R = 350 PHL 350 30 20 -40 - TEMPERATURE (˚C) A © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 Fig. 6 Low Level Output Current vs. Temperature - 100 Fig. 8 Propagation Delay vs. Pulse Input Current & 100 5 Page HIGH SPEED-10 MBit 0.6V ...

Page 7

... 7.5mA ELH ELH R = 350 EHL 350 & -40 - TEMPERATURE (˚C) A Fig. 11 Typical Pulse Width Distortion vs. Temperature © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 Fig. 10 Typical Rise and Fall Time vs. Temperature 240 200 160 120 100 - 7.5mA 350 -40 - TEMPERATURE (˚C) A Page ...

Page 8

... HCPL-0600 Pulse Generator tr = 5ns Input 3 Monitor ( Fig. 12 Test Circuit and W Pulse Generator tr = 5ns 7 © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 + bypass Output GND Test Circuit and W T aveforms for t Input Monitor ( + .1µf bypass Output GND Fig. 13 Test Circuit t Test Circuit t ...

Page 9

... HCPL-0600 0.5 V Fig. 14 Test Circuit Common Mode T Test Circuit Common Mode T T © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 .1µf bypass GND V CM Pulse Gen Peak Switching Pos. (A (Min (Max) O Switching Pos Page HIGH SPEED-10 MBit/s +5V 350 Output ...

Page 10

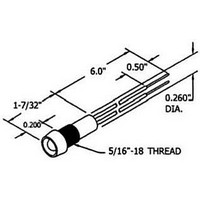

... HCPL-0600 8-Pin Small Outline 0.024 (0.61) 0.275 (6.99) 0.155 (3.94) © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 0.060 (1.52) 0.050 (1.27) Page HIGH SPEED-10 MBit/s 1/7/04 ...

Page 11

... ORDERING INFORMATION Order Option Identifi MARKING INFORMATION Definitions © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 Entry .R1 .R2 1 0600 Fairchild logo Device number VDE mark (Note: Only appears on parts ordered with VDE option – See order entry table) One digit year code, e.g., ‘3’ ...

Page 12

... Ramp up = 2–10 C/sec 0.5 1 1.5 2 Time (Minute) © 2004 Fairchild Semiconductor Corporation LOGIC GATE OPTOCOUPLERS HCPL-0601 8.0 0.1 2 0.05 4.0 0.1 6.4 0.2 230 C, 10–30 s • Peak reflow temperature: 245 C (package surface temperature) • Time of temperature higher than 183 C for 120–180 seconds • ...

Page 13

... Fairchild Semiconductor Corporation HIGH SPEED-10 MBit/s LOGIC GATE OPTOCOUPLERS HCPL-0601 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system affect its safety or effectiveness. ...