ADSP-21369KBPZ-3A Analog Devices Inc, ADSP-21369KBPZ-3A Datasheet - Page 44

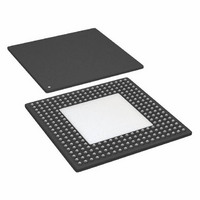

ADSP-21369KBPZ-3A

Manufacturer Part Number

ADSP-21369KBPZ-3A

Description

IC,DSP,32-BIT,CMOS,BGA,256PIN,PLASTIC

Manufacturer

Analog Devices Inc

Series

SHARC®r

Type

Floating Pointr

Datasheet

1.ADSP-21369KBPZ-2A.pdf

(60 pages)

Specifications of ADSP-21369KBPZ-3A

Interface

DAI, DPI

Clock Rate

400MHz

Non-volatile Memory

ROM (768 kB)

On-chip Ram

256kB

Voltage - I/o

3.30V

Voltage - Core

1.20V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

256-BGA Exposed Pad, 256-eBGA, 256-HBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

ADZS-21369-EZLITE - KIT EVAL EZ LITE ADDS-21369

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADSP-21369KBPZ-3A

Manufacturer:

TOREX

Quantity:

6 700

Company:

Part Number:

ADSP-21369KBPZ-3A

Manufacturer:

Analog Devices Inc

Quantity:

10 000

Part Number:

ADSP-21369KBPZ-3A

Manufacturer:

ADI/亚德诺

Quantity:

20 000

ADSP-21367/ADSP-21368/ADSP-21369

S/PDIF Receiver

The following section describes timing as it relates to the

S/PDIF receiver.

Internal Digital PLL Mode

In the internal digital phase-locked loop mode the internal PLL

(digital PLL) generates the 512 × FS clock.

Table 39. S/PDIF Receiver Internal Digital PLL Mode Timing

1

Parameter

Switching Characteristics

t

t

t

t

t

SCLK frequency is 64 × FS where FS = the frequency of LRCLK.

DFSI

HOFSI

DDTI

HDTI

SCLKIW

1

LRCLK Delay After SCLK

LRCLK Hold After SCLK

Transmit Data Delay After SCLK

Transmit Data Hold After SCLK

Transmit SCLK Width

(DATA CHANNEL

DAI_P20–1

DAI_P20–1

DAI_P20–1

(SCLK)

A/B)

(FS)

Figure 34. S/PDIF Receiver Internal Digital PLL Mode Timing

DRIVE EDGE

t

t

HOFSI

Rev. E | Page 44 of 60 | July 2009

HDTI

t

t

DDTI

DFSI

t

SCLKIW

Min

–2

–2

40

SAMPLE EDGE

5

Max

5

Unit

ns

ns

ns

ns

ns