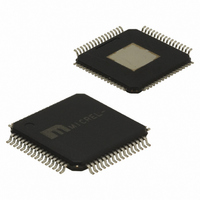

SY87721LHG Micrel Inc, SY87721LHG Datasheet - Page 6

SY87721LHG

Manufacturer Part Number

SY87721LHG

Description

IC CLOCK/DATA RECOVERY 64-TQFP

Manufacturer

Micrel Inc

Type

Clock and Data Recovery (CDR)r

Datasheet

1.SY87721LHY.pdf

(16 pages)

Specifications of SY87721LHG

Input

Differential

Output

Differential

Frequency - Max

340MHz

Voltage - Supply

3.15 V ~ 3.45 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

64-TQFP Exposed Pad, 64-eTQFP, 64-HTQFP, 64-VQFP

Frequency-max

340MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Micrel, Inc.

OUTPUTS

BRD [Buffered Recovered Data] – Differential CML Output

depending on the state of the BRDMX input. This allows a

user to selectively bypass the CDR or not, as warranted by

architecture. This CML output has a voltage swing of 400mV

loaded.

LFIN [Link Fault Indicate] – O.C. TTL Output

RDIN. Active HIGH indicates that the internal clock recovery

PLL has locked onto the incoming data stream. LFIN will go

HIGH if CD is HIGH and RDIN is within the frequency range

of the Receive PLL (as per ALRSEL). LFIN is an

asynchronous output.

RDOUTE [Receive Data Out] – Differential PECL Output

the recovered data from the input data stream (RDIN). It is

specified on the rising edge of RCLK.

RDOUTC [Receive Data Out] – Differential CML Output

RCLKE [Receive Clock Out] – Differential PECL Output

the recovered clock used to sample the recovered data

(RDOUT).

RCLKC [Receive Clock Out] – Differential CML Output

TCLKE [Transmit Clock Out] – Differential PECL Output

either the recovered clock (CLKSEL = HIGH) used to sample

the recovered data (RDOUT) or the transmit clock of the

frequency synthesizer (CLKSEL = LOW).

TCLKC [Transmit Clock Out] – Differential CML Output

PLLSN+, PLLSN– [Clock Synthesis Loop Filter]

band PLL.

PLLSW+, PLLSW– [Clock Synthesis Loop Filter]

M9999-012508

hbwhelp@micrel.com or (408) 955-1690

The signal is either a buffered RDIN

This output indicates the status of the input data stream

These ECL 100K outputs (+3.3V referenced) represent

This is the CML version of RDOUTE .

These ECL 100K outputs (+3.3V referenced) represent

This is the CML version of RCLKE .

These ECL 100K outputs (+3.3V referenced) represent

This is the CML version of TCLKE .

External loop filter pins for the clock synthesis narrow

or RDOUTC ,

6

PLL.

PLLRN+, PLLRN– [Clock Recovery Loop Filter]

band PLL.

PLLRW+, PLLRW– [Clock Recovery Loop Filter]

PLL.

OTHERS

VCC

VCCO

VCCA

GND

GNDA

NC

External loop filter pins for the clock synthesis wide band

External loop filter pins for the clock recovery narrow

External loop filter pins for the clock recovery wide band

Supply Voltage

Output Supply Voltage

Analog Supply Voltage

Ground

Analog Ground

These pins are for factory test, and are to be

left unconnected during normal use.

SY87721L