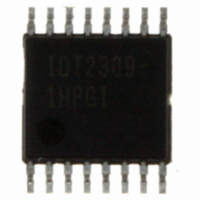

IDT2309-1HPGI IDT, Integrated Device Technology Inc, IDT2309-1HPGI Datasheet - Page 6

IDT2309-1HPGI

Manufacturer Part Number

IDT2309-1HPGI

Description

IC CLK BUFF ZD PLL HIDRV 16TSSOP

Manufacturer

IDT, Integrated Device Technology Inc

Type

Zero Delay Bufferr

Datasheet

1.IDT2309-1HPGI.pdf

(10 pages)

Specifications of IDT2309-1HPGI

Pll

Yes with Bypass

Input

LVTTL

Output

LVTTL

Number Of Circuits

1

Ratio - Input:output

1:9

Differential - Input:output

No/No

Frequency - Max

133MHz

Divider/multiplier

No/No

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

16-TSSOP

Frequency-max

133MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

2309-1HPGI

800-1297

800-1297

ZERO DELAY AND SKEW CONTROL

loading can affect and adjust the input/output delay. The Output Load Difference diagram illustrates the PLL's relative loading with respect to the other

outputs that can adjust the Input-Output (I/O) Delay.

load equal to that on the other outputs in order to obtain true zero I/O Delay. If I/O Delay adjustments are needed, use the Output Load Difference diagram

to calculate loading differences between the CLKOUT pin and other outputs. For zero output-to-output skew, all outputs must be loaded equally.

IDT2309

3.3V ZERO DELAY CLOCK BUFFER

For designs utilizing zero I/O Delay, all outputs including CLKOUT must be equally loaded. Even if the output is not used, it must have a capacitive

All outputs should be uniformly loaded in order to achieve Zero I/O Delay. Since the CLKOUT pin is the internal feedback for the PLL, its relative

-1000

-1500

1500

1000

-500

500

0

REF TO CLKA/CLKB RELAY vs. OUTPUT LOAD DIFFERENCE BETWEEN CLKOUT PIN AND CLKA/CLKB PINS

-30

-25

OUTPUT LOAD DIFFERENCE BETWEEN CLKOUT PIN AND CLKA/CLKB PINS (pF)

-20

-15

-10

-5

6

0

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

5

10

15

20

25

30