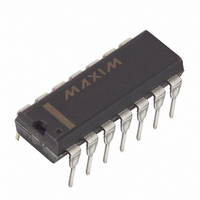

DS1801+ Maxim Integrated Products, DS1801+ Datasheet

DS1801+

Specifications of DS1801+

Related parts for DS1801+

DS1801+ Summary of contents

Page 1

FEATURES Ultra-low power consumption Operates from supplies Two digitally controlled, 65-position potentiometers including mute Logarithmic resistive characteristics (1 dB per step) Zero-crossing detection eliminates noise caused by wiper movement Serial port provides means for setting and ...

Page 2

OPERATION The DS1801 provides two 65-position potentiometers per package, each having a logarithmic resistive characteristic as shown in Table 1. The DS1801 is controlled by a 3-wire serial interface. The 3-wire serial interface is designed for CPU-controlled applications and allows ...

Page 3

SERIAL INTERFACE CONTROL Communication and control of the DS1801 is accomplished through a 3-wire serial port interface that drives an internal control logic unit. The 3-wire serial interface is designed for microprocessor or microcontroller applications. The interface consists of ...

Page 4

TIMING DIAGRAMS Figure DS1801 ...

Page 5

CASCADE OPERATION A feature of the DS1801 is the ability to control multiple devices from a single processor. Multiple DS1801s can be linked or daisy-chained as shown in Figure data bit is entered into the I/O shift ...

Page 6

TYPICAL SUPPLY CURRENT VS. SERIAL CLOCK RATE Figure DS1801 ...

Page 7

ABSOLUTE MAXIMUM RATINGS* Voltage on Any Pin Relative to Ground Operating Temperature Storage Temperature Soldering Temperature * This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the ...

Page 8

ANALOG RESISTOR CHARACTERISTICS (- + PARAMETER End to End Resistor Tolerance Absolute Tolerance Interchannel Matching Tap-to-Tap Tolerance -3 dB Cutoff Frequency Temperature Coefficient Total Harmonic Distortion (V = kHz, Tap RMS dB) ...

Page 9

AC ELECTRICAL CHARACTERISTICS PARAMETER CLK Frequency Width of CLK Pulse Data Setup Time Data Hold Time Propagation Delay Time Low to High Level Clock to Output Propagation Delay Time Low to High Level High to Clock Input High RST Low ...

Page 10

DIGITAL OUTPUT LOAD Figure 6 INTERNAL GROUND CONNECTIONS Figure 7 NOTE: GND and AGND must be tied to the same voltage level. DS1801 ORDERING INFORMATION ORDERING INFORMATION DS1801 DS1801E 14L TSSOP (173-mil) DS1801S 16L SOIC (300-mil) PACKAGE OPERATING TEMPERATURE 14L ...