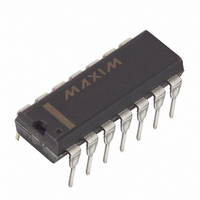

DS1868-100+ Maxim Integrated Products, DS1868-100+ Datasheet

DS1868-100+

Specifications of DS1868-100+

Related parts for DS1868-100+

DS1868-100+ Summary of contents

Page 1

... Industrial: -40°C to 85°C DESCRIPTION The DS1868 Dual Digital Potentiometer Chip consists of two digitally controlled solid-state potentiometers. Each potentiometer is composed of 256 resistive sections. Between each resistive section and both ends of the potentiometer are tap points which are accessible to the wiper. The position of the ...

Page 2

... CLK signal inputs. Three-wire serial timing requirements are provided in the timing diagrams of Figure 9(b),(c). Data written to the DS1868 over the 3-wire serial interface is stored in the 17-bit I/O shift register (see Figure 2). The 17-bit I/O shift register contains both 8-bit potentiometer wiper position values and the stack select bit ...

Page 3

... STACKED CONFIGURATION The potentiometers of the DS1868 can be connected in series as shown in Figure 3. This is referred to as the stacked configuration and allows the user to double the total end-to-end resistance of the part. The resolution of the combined potentiometers will remain the same as a single potentiometer but with a total of 512 wiper positions available ...

Page 4

... If the stack select bit has value 1, the multiplexed output, S potentiometer-1 wiper DS1868 , will be that of the OUT ...

Page 5

... CASCADE OPERATION A feature of the DS1868 is the ability to control multiple devices from a single processor. Multiple DS1868s can be linked or daisy chained as shown in Figure data bit is entered into the I/O shift register of the DS1868 a bit will appear at the C stack select bit of the DS1868 will always be the first out the part at the beginning of a transaction. The ...

Page 6

... Relative linearity is a measure of error between two adjacent wiper position points and is given in terms equation (2). (2) RELATIVE LINEARITY Figure plot of absolute linearity and relative linearity versus wiper position for the DS1868 The specification for absolute linearity of the DS1868 is 0.75 MI typical. The specification for relative linearity of the DS1868 is 0.3 MI typical. LINEARITY MEASUREMENT CONFIGURATION Figure 5 ...

Page 7

... DS1868 ABSOLUTE AND RELATIVE LINEARITY Figure 6 TYPICAL APPLICATION CONFIGURATIONS Figures 7 and 8 show two typical application configurations for the DS1868. By connecting the wiper terminal of the part to a high impedance load, the effects of the wiper resistance is minimized, since the wiper resistance can vary from 400 to 1000 ohms, depending on wiper voltage. Figure 7 presents the device connected in a variable gain amplifier ...

Page 8

... VARIABLE GAIN AMPLIFIER Figure 7 FIXED GAIN ATTENUATOR Figure DS1868 ...

Page 9

... GND GND -0 -3 SYMBOL MIN TYP 400 STBY (- + SYMBOL MIN TYP -20 0.75 0.3 F CUTOFF 750 DS1868 -1.0V to +7.0V -3.3V to +4.7V - +85 C -55°C to +125°C 260°C for 10 seconds =5.0V 10%) CC MAX UNITS NOTES GND +0 GND =5.0V 10%) CC MAX UNITS ...

Page 10

... DS1868 ...

Page 11

... Relative linearity is used to determine the change in voltage between successive tap positions. Device test limits 0.5 LSB. 6. Typical values are for and nominal supply voltage cutoff frequency characteristics for the DS1868 depend on potentiometer total resistance: DS1868-010; 1 MHz, DS1868-050; 200 kHz; and DS1868-100; 80 kHz. 8. Cout is active regardless of the state 1.5 volts. ...

Page 12

... TIMING DIAGRAMS Figure 9 (a) 3-Wire Serial Interface General Overview (b) Start of Communication Transaction (c) End of Communication Transaction DS1868 ...

Page 13

... DIGITAL OUTPUT LOAD SCHEMATIC Figure 10 TYPICAL SUPPLY CURRENT VS. SERIAL CLOCK RATE Figure DS1868 ...

Page 14

... DS1868 20-PIN TSSOP DIM MIN MAX 1. 0. 0.75 1. 0.09 0. 0.50 0. 0.65 BSC B MM 0.18 0. 6.40 6. 4.40 NOM G MM 0.25 REF H MM 6.25 6.55 phi DS1868 ...