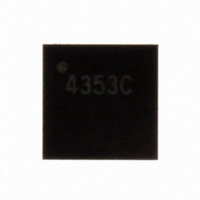

CS4353-CNZ Cirrus Logic Inc, CS4353-CNZ Datasheet - Page 14

CS4353-CNZ

Manufacturer Part Number

CS4353-CNZ

Description

IC DAC STER 106DB 2VRMS 24QFN

Manufacturer

Cirrus Logic Inc

Datasheet

1.CS4353-CNZ.pdf

(26 pages)

Specifications of CS4353-CNZ

Number Of Converters

1

Package / Case

24-QFN

Number Of Bits

24

Data Interface

Serial

Voltage Supply Source

Single Supply

Power Dissipation (max)

152mW

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Number Of Dac Outputs

2

Resolution

24 bit

Interface Type

Serial

Supply Voltage (max)

3.47 V

Supply Voltage (min)

3.13 V

Maximum Operating Temperature

+ 125 C

Mounting Style

SMD/SMT

Maximum Power Dissipation

152 mW

Minimum Operating Temperature

- 55 C

Supply Current

10 mA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1519 - BOARD EVAL FOR CS4353 DAC

Settling Time

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

598-1640

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS4353-CNZ

Manufacturer:

CIRRUS

Quantity:

4 588

Part Number:

CS4353-CNZ

Manufacturer:

CIRRUS

Quantity:

20 000

Company:

Part Number:

CS4353-CNZR

Manufacturer:

TI

Quantity:

600

Part Number:

CS4353-CNZR

Manufacturer:

CIRRUS

Quantity:

20 000

14

4.2

4.3

Sample Rate

Sample Rate Range/Operational Mode Detect

The CS4353 operates in one of three operational modes. The device will auto-detect the correct mode when

the input sample rate (Fs), defined by the LRCK frequency, falls within one of the ranges illustrated in

Table

LRCK frequency, a valid serial clock (SCLK) and master clock (MCLK) must also be applied to the device

for speed mode auto-detection; see

System Clocking

The device requires external generation of the master (MCLK), left/right (LRCK) and serial (SCLK) clocks.

The left/right clock, defined also as the input sample rate (Fs), must be synchronously derived from the

MCLK signal according to specified ratios. The specified ratios of MCLK to LRCK, along with several stan-

dard audio sample rates and the required MCLK frequency, are illustrated in

Refer to

to

Sample Rate

(kHz)

“Switching Specifications - Serial Audio Interface” on page 9

88.2

96

(kHz)

44.1

32

48

2. Sample rates outside the specified range for each mode are not supported. In addition to a valid

Section 4.4

Input Sample Rate (Fs)

Sample Rate

170 kHz - 216 kHz

84 kHz - 108 kHz

11.2896

12.2880

8 kHz - 54 kHz

128x

for the required SCLK timing associated with the selected Digital Interface Format and

(kHz)

176.4

11.2896

12.2880

192

8.1920

256x

Table 4. Double-speed Mode Standard Frequencies

Table 3. Single-speed Mode Standard Frequencies

Table 5. Quad-speed Mode Standard Frequencies

Table 2. CS4353 Operational Mode Auto-Detect

Figure

16.9344

18.4320

192x

12.2880

16.9344

18.4320

384x

22.5792

24.5760

128x

9.

MCLK (MHz)

MCLK (MHz)

MCLK (MHz)

22.5792

24.5760

16.3840

22.5792

24.5760

256x

512x

33.8688

36.8640

192x

for the maximum allowed clock frequencies.

Double-Speed Mode

Single-Speed Mode

Quad-Speed Mode

33.8688

36.8640

24.5760

33.8688

36.8640

384x

45.1584

49.1520

768x

256x

Mode

Tables

3-5.

45.1584

49.1520

32.7680

45.1584

49.1520

1024x

512x

CS4353

DS803F1