XC4005E-3PQ100I Xilinx Inc, XC4005E-3PQ100I Datasheet - Page 59

XC4005E-3PQ100I

Manufacturer Part Number

XC4005E-3PQ100I

Description

IC FPGA I-TEMP 5V 3-SPD 100-PQFP

Manufacturer

Xilinx Inc

Series

XC4000E/Xr

Datasheet

1.XC4005E-4PC84C.pdf

(68 pages)

Specifications of XC4005E-3PQ100I

Number Of Logic Elements/cells

466

Number Of Labs/clbs

196

Total Ram Bits

6272

Number Of I /o

77

Number Of Gates

5000

Voltage - Supply

4.5 V ~ 5.5 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

100-BQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC4005E-3PQ100I

Manufacturer:

XILINX

Quantity:

695

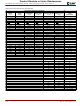

Figure 55: Master Parallel Mode Programming Switching Characteristics

May 14, 1999 (Version 1.6)

Notes: 1. At power-up, Vcc must rise from 2.0 V to Vcc min in less than 25 ms, otherwise delay configuration by pulling PROGRAM

This timing diagram shows that the EPROM requirements are extremely relaxed. EPROM access time can be longer than

500 ns. EPROM data output has no hold-time requirements.

(output)

(output)

(output)

(output)

A0-A17

D0-D7

DOUT

RCLK

CCLK

RCLK

2. The first Data byte is loaded and CCLK starts at the end of the first RCLK active cycle (rising edge).

Low until Vcc is valid.

R

Delay to Address valid

Data setup time

Data hold time

Product Obsolete or Under Obsolescence

Description

XC4000E and XC4000X Series Field Programmable Gate Arrays

Address for Byte n

1

2

3

Symbol

7 CCLKs

T

T

T

DRC

RCD

RAC

2 T

Byte

DRC

Min

60

0

0

Byte n - 1

D6

Address for Byte n + 1

1 T

3 T

CCLK

RAC

Max

RCD

200

D7

Units

ns

ns

ns

X6078

6-63

6