CS42L73-CWZR Cirrus Logic Inc, CS42L73-CWZR Datasheet - Page 3

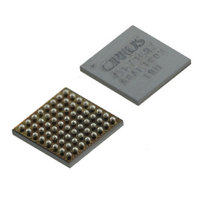

CS42L73-CWZR

Manufacturer Part Number

CS42L73-CWZR

Description

IC CODEC AUDIO TELEPHONY 64WLCSP

Manufacturer

Cirrus Logic Inc

Type

Audio Codecr

Datasheet

1.CS42L73-CWZR.pdf

(7 pages)

Specifications of CS42L73-CWZR

Package / Case

64-WLCSP

Data Interface

I²C, Serial

Number Of Adcs / Dacs

2 / 1

Sigma Delta

No

Dynamic Range, Adcs / Dacs (db) Typ

91 / 94

Voltage - Supply, Analog

3 V ~ 5.25 V

Voltage - Supply, Digital

3 V ~ 5.25 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Number Of Dac Outputs

5

Interface Type

Serial (I2C)

Operating Supply Voltage

3 V to 5.25 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Channels

2

Thd Plus Noise

- 85 dB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

598-1802-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS42L73-CWZR

Manufacturer:

Cirrus Logic

Quantity:

135

General Description

The CS42L73 is a highly integrated, low-power, audio and telephony CODEC for portable applications such as

smartphones and ultra mobile personal computers.

The CS42L73 features a flexible clocking architecture, allowing the device to utilize reference clock frequencies

of 6, 12, 24, 13, 26, 19.2, or 38.4 MHz, or any standard audio master clock. Up to two reference/master clock sourc-

es may be connected; either one can be selected to drive the internal clocks and processing rate of the CS42L73.

Thus, multiple master clock sources within a system can be dynamically activated and de-activated to minimize sys-

tem-level power consumption.

Three asynchronous bidirectional serial ports (Auxiliary, Audio, and Voice Serial Ports) support multiple clock

domains of various digital audio sources or destinations. Three low-latency, fast-locking, integrated high-perfor-

mance asynchronous sample rate converters synchronize and convert the audio samples to the internal

processing rate of the CS42L73.

A stereo line input or two mono (one stereo) microphone (MIC) inputs are routed to a stereo ADC. The MIC inputs

may be selectively pre-amplified by +10 or +20 dB. Two independent, low-noise MIC bias voltage supplies are also

provided. A programmable gain amplifier (PGA) is applied to the inputs before they reach the ADC.

The stereo input path that follows the stereo ADC begins with a multiplexer to selectively choose data from a dig-

ital MIC interface. Following the multiplexer, the data is decimated, selectively DC high-pass filtered, channel-

swapped or mono-to-stereo routed (fanned-out), and volume adjusted or muted. The volume levels can be automat-

ically adjusted via a programmable Automatic Level Control (ALC) and noise gate.

A digital mixer is utilized to mix and route the CS42L73’s inputs (analog inputs to ADC, digital MIC, or serial ports)

to outputs (DAC-fed amplifiers or serial ports). There is independent attenuation on each mixer input for each output.

The processing along the output paths from the digital mixer to the two stereo DACs includes volume adjustment

and mute control. A peak-detector can be used to automatically adjust the volume levels via a programmable limiter.

The first stereo DAC feeds the stereo headphone and line output amplifiers, which are powered from a dedicated

positive supply. An integrated charge pump provides a negative supply. This allows a ground-centered analog out-

put with a wide signal swing, and eliminates external DC-blocking capacitors while reducing pops and clicks. Tri-

level Class-H amplification is utilized to reduce power consumption under low-signal-level conditions. Analog vol-

ume controls are provided on the stereo headphone and line outputs.

The second stereo DAC feeds several mono outputs. The left channel of the DAC sources a mono, differential-

drive, speakerphone amplifier for driving the handset speakerphone. The right channel sources a mono, differ-

ential-drive, earphone amplifier for driving the handset earphone. The right channel is also routed to a mono,

differential-drive, speakerphone line output, which may be connected to an external amplifier to implement a ste-

reo speakerphone configuration when it is used in conjunction with the integrated speakerphone amplifier.

The CS42L73 implements robust power management to achieve ultra-low power consumption. High granularity

The CS42L73 is available in space-saving 64-ball WLCSP and 65-ball FBGA packages for the commercial (-40° to

+85° C) grade.

in power-down controls allows individual functional blocks to be powered down when unused. The internal low drop-

out regulator (LDO) saves power by running the internal digital circuits at half the logic interface supply voltage

(VL/2). In a system with an existing high-efficiency supply at VL/2, the internal LDO may be disabled and the digital

circuits powered directly by the external VL/2 supply.

A high-speed I²C control port interface capable of up to 400 kHz operation facilitates register programming.

CS42L73

3